# Power Quality Assessment of Solar Inverters Connected With Utility Grid/Micro-Grid

A Thesis Submitted

in Partial Fulfilment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

by

## Baibhav Kumar Gupta

(2017 eez 0009)

### DEPARTMENT OF ELECTRICAL ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY ROPAR

August, 2022

Baibhav Kumar Gupta: Power Quality Assessment of Solar Inverters Connected With Utility Grid/Micro-Grid Copyright ©2022, Indian Institute of Technology Ropar All Rights Reserved To My Parents

### **Declaration of Originality**

I hereby declare that the work which is being presented in the thesis entitled "Power Quality Assessment of Solar Inverters Connected With Utility Grid/Micro-Grid" has been solely authored by me. It presents the result of my own independent investigation/research conducted during the time period from  $5^{th}$  January 2018 to 10<sup>th</sup> August 2022 under the supervision of **Dr. K. Ramachandra Sekhar**, Assistant professor, Indian Institute of Technology Ropar. To the best of my knowledge, it is an original work, both in terms of research content and narrative, and has not been submitted or accepted elsewhere, in part or in full, for the award of any degree, diploma, fellowship, associateship, or similar title of any university or institution. I also declare that any idea/data/fact/source stated in my thesis has not been fabricated/ falsified/ misrepresented. All the principles of academic honesty and integrity have been followed. I fully understand that if the thesis is found to be unoriginal, fabricated, or plagiarized, the Institute reserves the right to withdraw the thesis from its archive and revoke the associated Degree conferred. Additionally, the Institute also reserves the right to appraise all concerned sections of society of the matter for their information and necessary action (if any). If accepted, I hereby consent for my thesis to be available online in the Institute's Open Access repository, inter-library loan, and the title & abstract to be made available to outside organizations.

Name: Baibhav Kumar Gupta Entry Number: 2017EEZ0009 Program: PhD Department: Electrical Engineering Indian Institute of Technology Ropar Rupnagar, Punjab 140001

Date: 10-08-2022

### Acknowledgement

I take this opportunity to acknowledge my heartfelt gratitude to all those people who directly or indirectly helped me to carry out this research work successfully. I am heartily thankful to my supervisor, Dr.K. Ramachandra Sekhar, whose encouragement, guidance and support through out my research work enabled me to develop an understanding of the subject. I appreciate his sincere help in terms of contributions of time, ideas so as to make my Ph.D. experience stimulating and productive. The joy and enthusiasm that he has for his research was contagious and motivational for me, even during tough times in the Ph.D. pursuit. I express my gratitude for his willingness to help and timely advices on issues, even beyond the scope of doctoral studies.

I would like to acknowledge the financial, academic and technical support of the Indian Institute of Technology Ropar for this research. I am sincerely grateful to Dr. A. V Raviteja, Dr. Bibhu Prasad Padhy and Dr. Mukesh Kumar for assessing the work and giving invaluable suggestions as members of Doctoral committee.

The members of the Power Group have contributed immensely to my personal and professional time during my stay in the institute. The group has been a source of friendships as well as good advice and collaboration. I especially thank Mr. Mahesh Reddy Pundru, Mr. Amol Ishwarrao Gedam, Mr. Aashish Kumar, Mr. Nikhil Kumar, Mr. A. Suryakiran, Mr. Sahil Sharma, Mr. Digamber kumar, Mr. Mahetab Alam ,Mr. Manish Kumar, Mr. Vaibhav Sah and Mr. Muddasani Satyanarayana for their valuable advices during my course of research and personal life. I would like to express gratitude to the services being offered by Mr.Devendra, Mr. Dilbag, Mr.Jaspreet staff of power electronics and Machine laboratory of Electrical Engineering department. Last but not the least I would like to thank my family, my parents who educated me, for always believing in my capabilities and for encouraging me to pursue my dreams. Especially my father, for unconditional support and encouragement, for listening to all my problems and frustrations very patiently and for always being there for me during good and bad times.

### Certificate

This is to certify that the thesis entitled "Power Quality Assessment of Solar Inverters Connected With Utility Grid/Micro-Grid", submitted by Baibhav Kumar Gupta (2017EEZ0009) for the award of the degree of Doctor of Philosophy of Indian Institute of Technology Ropar, is a record of bonafide research work carried out under my guidance and supervision. To the best of my knowledge and belief, the work presented in this thesis is original and has not been submitted, either in part or full, for the award of any other degree, diploma, fellowship, associateship or similar title of any university or institution.

In my opinion, the thesis has reached the standard fulfilling the requirements of the regulations relating to the Degree.

KRdse

Signature of the Supervisor Name: Dr. K. Ramachandra Sekhar Department: Electrical Engineering Indian Institute of Technology Ropar Rupnagar, Punjab 140001 Date: 10-08-2022

### Abstract

The Interface inverters arbitrate the network impedance based on the source characteristics for efficient solar energy harvesting. The wide impedance arbitration capability of the interface inverter defines the wide operational integrity with the AC network. In the weak grid scenario, the uncompensated grid inductance beyond PCC offers the negative damping for power oscillations at the point of common coupling (PCC) tugs the system towards instability. In this research work, the negative damping influence due to interactions between the system impedance (filter inductance and grid power injection resistance) and AC network impedance (grid inductance) on the inverter closed-loop controller is characterized by observing the natural phase deviations in real and imaginary axis. Through distinguished system's natural response, a novel second-order system impedance model is derived, and proposed current controller gain characterization aiming to achieve positive damping to mitigate the PCC's oscillations. Further tuning of the controller based on the natural response of the derived impedance model accomplishes the enhanced grid injected power quality. The efficacy of the derived system impedance model along with coherence of current controller gain is demonstrated on hardware for enhanced power quality under the stable operating region. Apart from this, a new series solar inverter configuration is proposed to share the power in terms of voltage, unlike parallel inverter configurations. In a single-stage parallel inverter, elevated DC potential and circulating current due to common-mode voltage (CMV) would degrade the solar inverter's life. The proposed topology eases the stress on the DC bus and protects the solar inverter from the issues associated with elevated DC potential (Potential induced degradation effect, switch operating voltage stress, etc.). The inherent boosting capability of the proposed series inverter with two modular inverters is demonstrated through two switching algorithms. In the first switching algorithm, the switching combinations are devised to yield the maximum voltage across the load. The second switching algorithm demonstrates the method of eliminating CMV by choosing the appropriate switching combination of two inverters. The eliminated instantaneous CMV would give the provision of operating proposed topology with common DC bus along with the flexibility of DC bus grounding. For the proposed configuration with devised switching techniques, the closed-loop controller is designed by computing the plant's equivalent characteristic impedance using a state-space model. The effectiveness of the proposed configuration, along with the closed-loop control, is validated through hardware. Also the multi boost solar inverter topologies of three variants are presented for grid connected applications. Since the proposed topologies aim to achieve higher voltage boost at AC side with reduced DC bus potential, it is required to use asynchronous switching strategies, unlike parallel inverter configurations. Although the proposed topologies are advantageous in-terms of improved reliability of solar panels and inverter modules, but instantaneous characteristic impedance imbalance due to asynchronous switching provokes circulating current within the inverter modules. Since the circulating current is undesirable concerning power quality and thermal aspects, in this research work,

the method of instantaneous impedance balance is ensured with the specially designed switching algorithm for proposed topologies. The eliminated instantaneous circulating current provide the flexibility of operating all inverter modules with the common DC bus. The proposed high gain boost configurations and switching methodologies are demonstrated on hardware prototype by pumping 2.4 kW power to the grid.

**Keywords**: Characteristic impedance, Circulating current, Closed loop controller modeling, Common DC Bus, Common mode voltage, Controller gains, Current THD, Distribution network, Grid-connected solar inverter, Grid impedance, Micro grid, Parallel inverter, Power quality, Reactive power compensation, series inverters, Small signal analysis, Solar inverter, Stability analysis, State space modeling, Virtual inertia, Voltage boost topology, Weak grid,

## List of Publications

### Patents

- Baibhav Kumar Gupta, Amol ishwarrao Gedam and K. Ramachandra Sekhar "suppressing circulating current through sequential switching of modular inverters in grid applications" Application number- 202011014453, Publication number-41/2021

- 2. Amol ishwarrao Gedam , Baibhav Kumar Gupta and K. Ramachandra Sekhar "a single stage voltage rectifier circuit for battery charging and a method of operating thereof" Application number- 202111016095.

- 3. K. Ramachandra Sekhar, Mahesh Reddy Pundru and Baibhav Kumar Gupta "system for optimizing dc voltages of inverter modules and a method thereof" Application number- 202211021950.

### Journals

- B. K. Gupta and S. R. Kondapalli, "A Current Controller Gain Characterization of Weak Grid Coupled Solar Inverter Through Impedance Interaction Modeling," in IEEE Transactions on Industrial Electronics, doi:10.1109/TIE.2022.3170633.

- B. K. Gupta, K. R. Sekhar and A. I. Gedam, "Solar Interfaced Series Inverter With Provision of Common DC Bus Grounding," in IEEE Transactions on Industrial Electronics, vol.69,no.4,pp.3656-3666, April 2022, doi:10.1109/TIE.2021.3073303.

- 3. B. K. Gupta, K. R. Sekhar and A. kumar, "A Novel Multi Gain Single-Stage Grid-Connected Inverter With Asynchronous Switching for Intra-Inverter Circulating Current Elimination," in IEEE Transactions on Power Electronics, 2022, doi: 10.1109/TPEL.2022.3193566.

#### Conferences

- K. R. Sekhar, B. K. Gupta and A. I. Gedam, "The Closed Loop Controller Gain Characterization for Enhanced Current Quality in Solar Inverters Coupled with Weak Grid," 2019 8th International Conference on Renewable Energy Research and Applications (ICRERA),2019,pp. 696-701, doi:10.1109/ICRERA47325.2019.8996644

- B. K. Gupta, A. I. Gedam and K. R. Sekhar, "A Dual Inverter Based Grid Connected Solar Power Conditioning System With Coordinated Closed Loop Control," 2019 IEEE Innovative Smart Grid Technologies-Asia (ISGT Asia), 2019, pp.2178-2183, doi:10.1109/ISGT-Asia.2019.8880886

- 3. B. K. Gupta, K. R. Sekhar and A. I. Gedam, "Balanced Per-Phase Sequential Switching to Suppress Circulating Current in Grid Connected Modular Solar Inverters," 2019 8th International Conference on Renewable Energy Research and Applications (ICRERA), 2019, pp. 686-691, doi: 10.1109/ICRERA47325.2019.8996838

- A. I. Gedam, B. Kumar Gupta and K. R. Sekhar, "Evaluation of DC Link Capacitor for Solar Fed Dual Inverter with Zero Sequence Elimination PWM," 2019 IEEE PES GTD Grand International Conference and Exposition Asia (GTD Asia), 2019, pp. 667-672, doi: 10.1109/GTDAsia.2019.8716014.

# Contents

| D             | eclar  | ration                                                                                | iv         |

|---------------|--------|---------------------------------------------------------------------------------------|------------|

| A             | ckno   | wledgement                                                                            | v          |

| C             | ertifi | icate                                                                                 | vi         |

| A             | bstra  | act                                                                                   | vii        |

| Li            | st of  | f Publications                                                                        | ix         |

| Li            | st of  | f Figures x                                                                           | iii        |

| $\mathbf{Li}$ | st of  | f Tables xv                                                                           | vii        |

| 1             | Int    | roduction                                                                             | 1          |

|               | 1.1    | Single Stage Grid Connected Inverter                                                  | 1          |

|               |        | 1.1.1 Power Quality Issues in Weak Grid Coupled Solar Inverter                        | 2          |

|               |        | 1.1.2 Elevated DC Bus Potential and Circulating Current Issues                        | 3          |

|               | 1.2    | Motivation                                                                            | 6          |

|               |        | 1.2.1 Year-Wise Installed Capacity of Energy Generation in India                      | 6          |

|               |        | 1.2.2 Government Initiatives to Promote Clean Energy Generation                       | 7          |

|               | 1.3    | Objectives                                                                            | 8          |

|               | 1.4    | Organization of the thesis                                                            | 9          |

| <b>2</b>      |        | Current Controller Gain Characterization of Weak Grid Coupled Solar                   |            |

|               |        |                                                                                       | 11         |

|               | 2.1    |                                                                                       | 11         |

|               | 2.2    |                                                                                       | 13         |

|               | 2.3    |                                                                                       | 16         |

|               | 2.4    |                                                                                       | 21         |

|               | 2.5    |                                                                                       | 22         |

|               |        |                                                                                       | 23         |

|               |        | 2.5.2 The demonstration of proposed controller gain characterization on               | റെ         |

|               |        |                                                                                       | 28         |

|               |        | 2.5.3 The % THD comparison at different grid inductance with varying controller gains | 31         |

|               | 2.6    |                                                                                       | 31         |

|               | 2.0    |                                                                                       | <b>J T</b> |

| 3  | Sola  | r Interfaced Series Inverter with Provision of Common DC bus                          |           |

|----|-------|---------------------------------------------------------------------------------------|-----------|

|    | Gro   | unding                                                                                | 33        |

|    | 3.1   | Series inverter configuration                                                         | 33        |

|    |       | 3.1.1 Operational evaluation of conventional parallel inverters                       | 35        |

|    |       | 3.1.2 The series configuration with Complementary switching                           | 36        |

|    |       | 3.1.3 The series configuration with per phase balanced switching algorithm            | 39        |

|    |       | 3.1.4 Closed-loop current controller design through state space analysis .            | 41        |

|    | 3.2   | Results and Discussions                                                               | 47        |

|    | 3.3   | Conclusion                                                                            | 51        |

| 4  | AI    | Novel Multi Gain Grid-Connected Inverter With Asynchronous                            | ,         |

|    | Swi   | tching for Intra-Inverter Circulating Current Elimination                             | <b>53</b> |

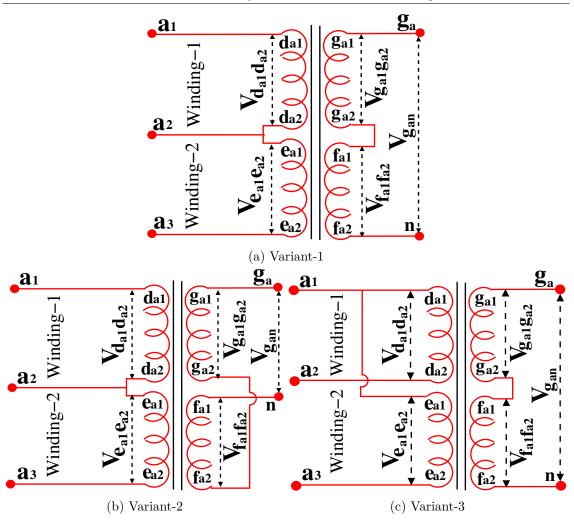

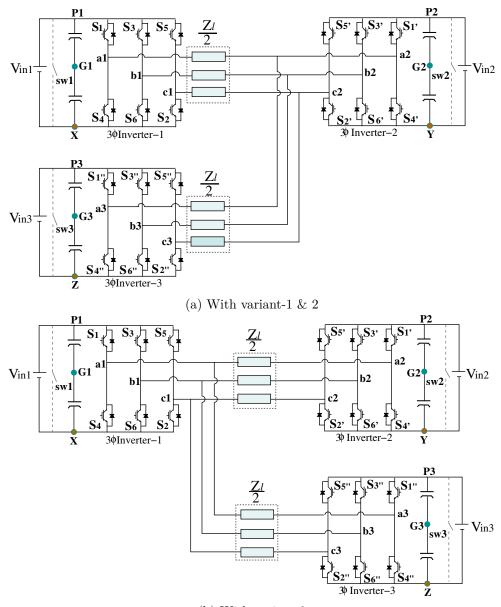

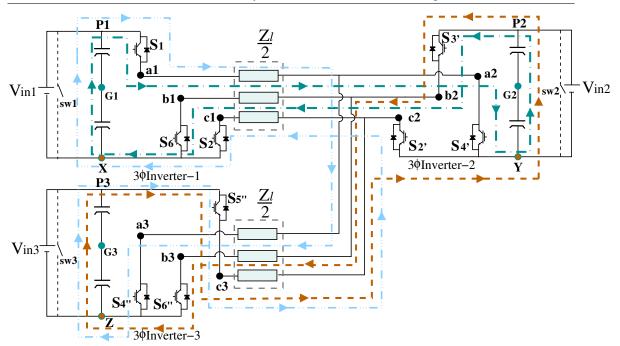

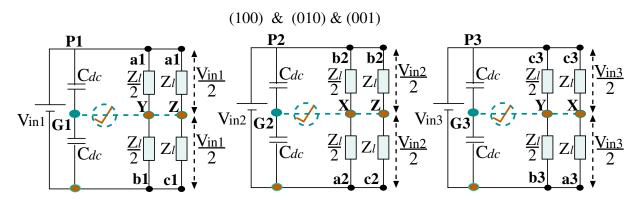

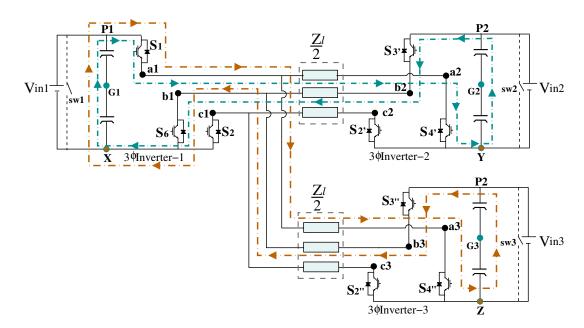

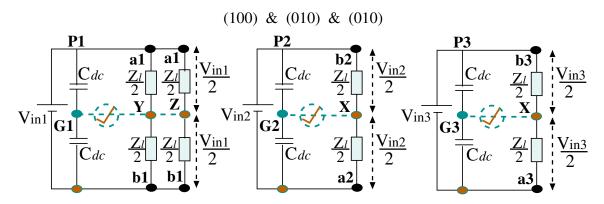

|    | 4.1   | The Proposed Multi gain voltage solar interface inverter                              | 53        |

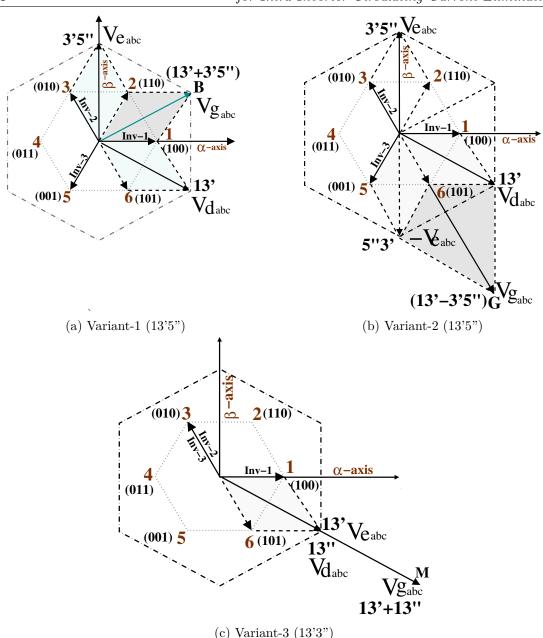

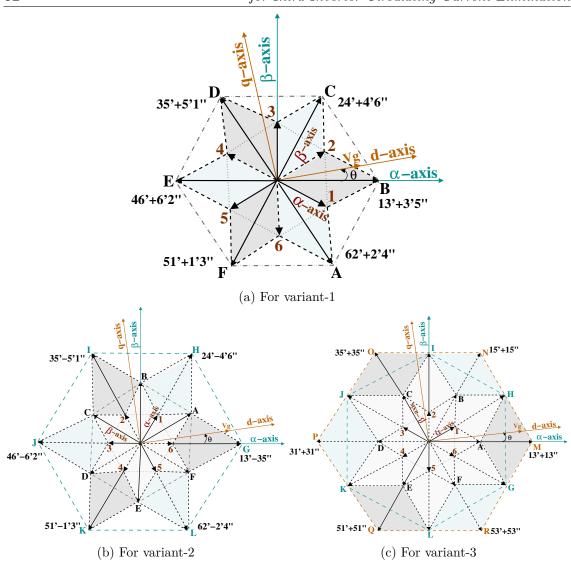

|    | 4.2   | The grid voltage realization through dynamic impedance balancing                      | 55        |

|    |       | 4.2.1 The switching sequence realization for variant-1 and variant-2                  | 55        |

|    |       | 4.2.2 The switching sequence realization for variant-3                                | 59        |

|    | 4.3   | The closed loop controller design through state space modeling $\ldots \ldots \ldots$ | 63        |

|    | 4.4   | Result and Discussion                                                                 | 68        |

|    | 4.5   | conclusion                                                                            | 78        |

| 5  | Con   | clusion                                                                               | 79        |

|    | 5.1   | Summary                                                                               | 79        |

|    | 5.2   | Scope of Future Research                                                              | 80        |

| Re | efere | nces                                                                                  | 81        |

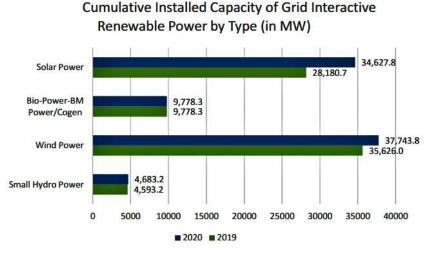

| 1.1  | Installed capacity of electricity generation in MW                                  | 7  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | Cumulative installed capacity of grid interactive renewable power by type           |    |

|      | (in MW) (X-axis: Renewable sources ; Y-axis: Energy generation in MW) .             | 8  |

| 2.1  | The circuit diagram of single stage grid connected inverter                         | 11 |

| 2.2  | The phasor diagram representing the stiff grid scenario                             | 12 |

| 2.3  | The simplified single line diagram to explain the weak grid scenario                | 13 |

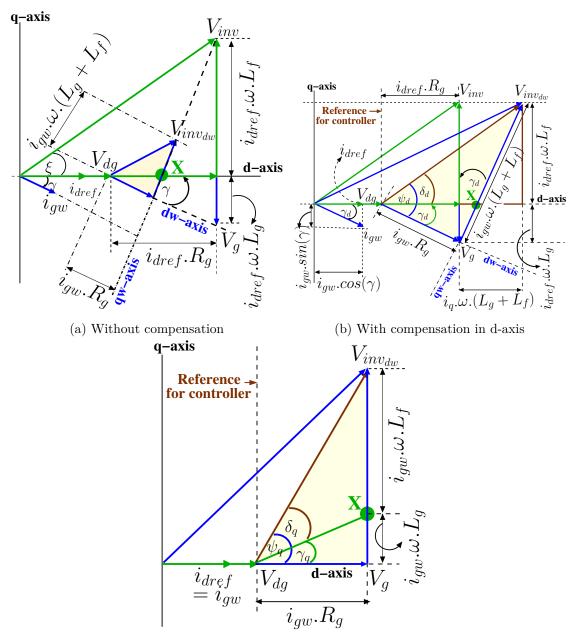

| 2.4  | The phasor diagram representing the inverter voltage, grid voltage and grid         |    |

|      | injected current in weak grid scenario                                              | 14 |

| 2.5  | The phasor diagram representing inverter voltage oscillations due to                |    |

|      | coupling between d-axis and q-axis compensation in weak grid scenario               | 16 |

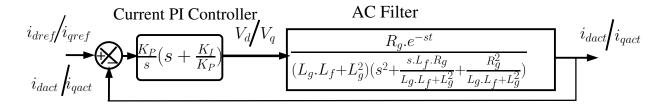

| 2.6  | The simplified closed loop representation with the identified system transfer       |    |

|      | function and linear controller                                                      | 16 |

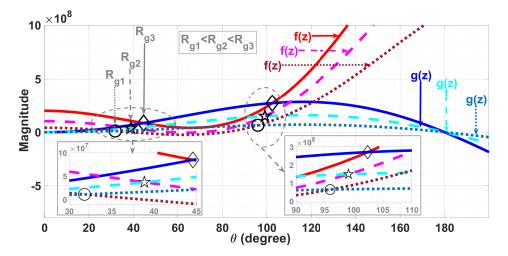

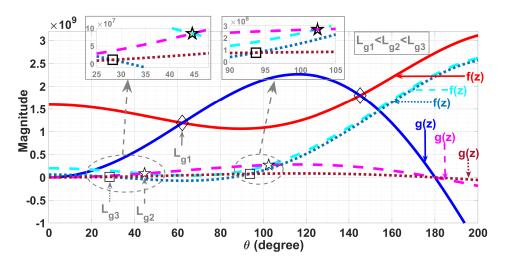

| 2.7  | The variations of $f(z)$ and $g(z)$ (mentioned in (2.19)) with varying              |    |

|      | resistance $(R_g)$ at a given filter inductance $(L_f)$ and grid inductance $(L_g)$ | 18 |

| 2.8  | The variations of $f(z)$ and $g(z)$ of (mentioned in (2.19)) with varying grid      |    |

|      | inductance $(L_g)$ at a given filter inductance $(L_f)$ and resistance $(R_g)$      | 18 |

| 2.9  | The variations of $f(z)$ and $g(z)$ (mentioned in (2.19)) with varying $K_p$ at     |    |

|      | given grid inductance $(L_g)$ , filter inductance $(L_f)$ and resistance $(R_g)$    | 19 |

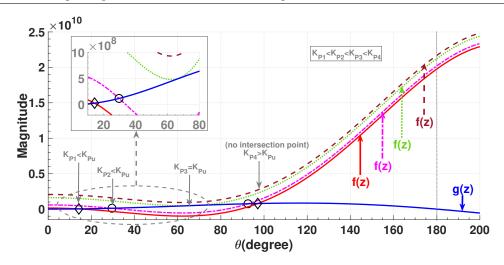

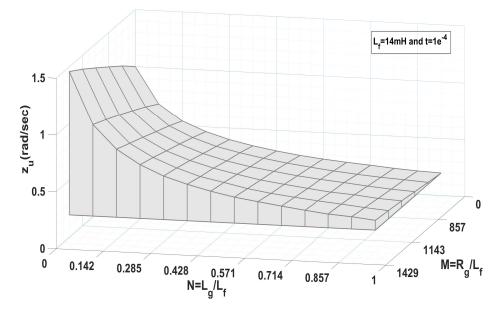

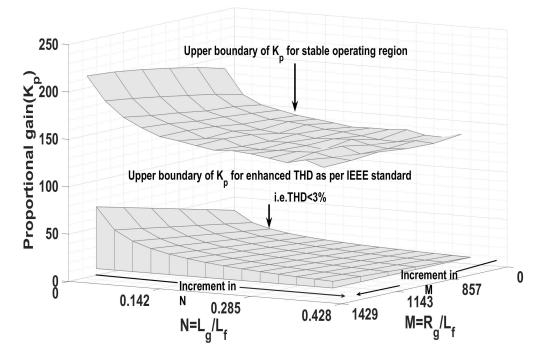

| 2.10 | The identified $z_u$ boundaries of stable region for different M and N values       | 20 |

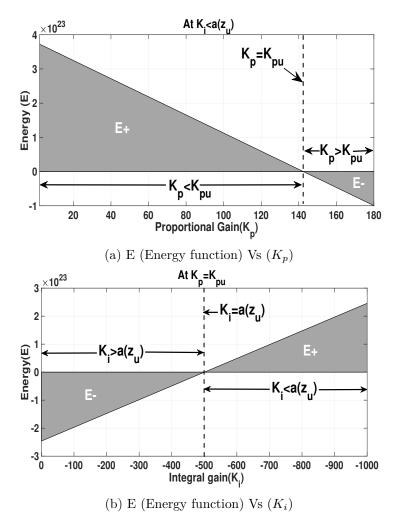

| 2.11 | The variation of energy function with reference to controller gains $\ldots$        | 20 |

| 2.12 | The identified proportional gain boundaries of stable region and augmented          |    |

|      | grid injected current quality region for different M and N values                   | 21 |

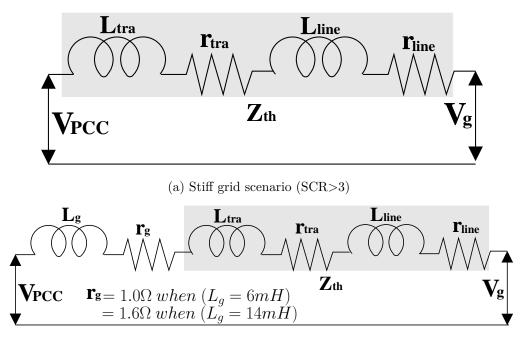

| 2.13 | The single line diagram representing the line impedance's between PCC and           |    |

|      | the grid                                                                            | 22 |

| 2.14 | The hardware prototype developed in lab for experimental validation                 | 23 |

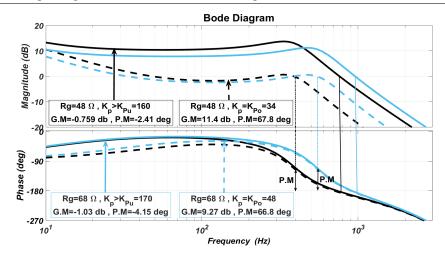

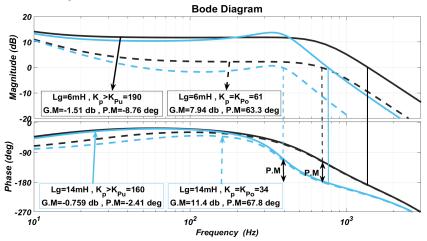

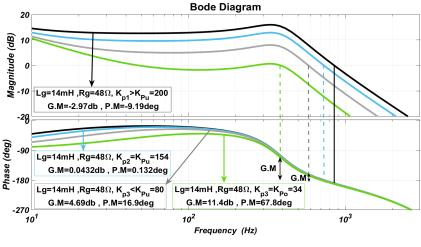

| 2.15 | Frequency response of the closed loop system shown in Fig.2.6                       | 25 |

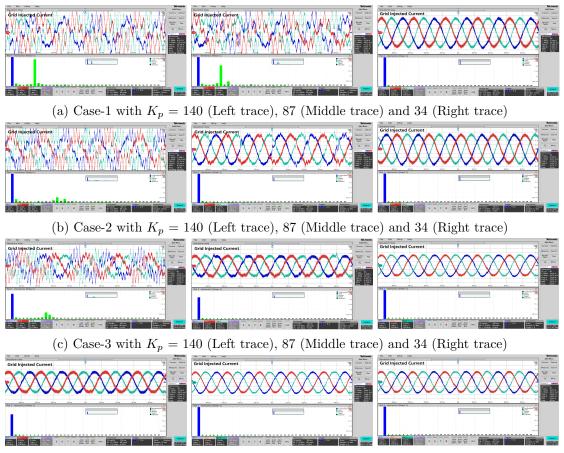

| 2.16 | The profile of Grid injected current (top)and corresponding current                 |    |

|      | harmonic spectrum (bottom bottom)                                                   | 26 |

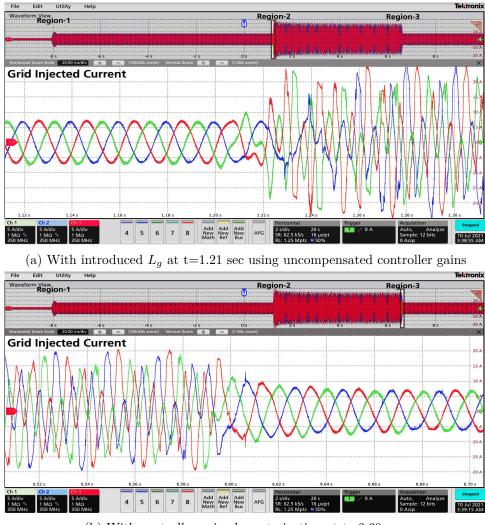

| 2.17 | The dynamic response of the grid injectd current in weak grid scenario with         |    |

|      | corresponding gain characterization                                                 | 27 |

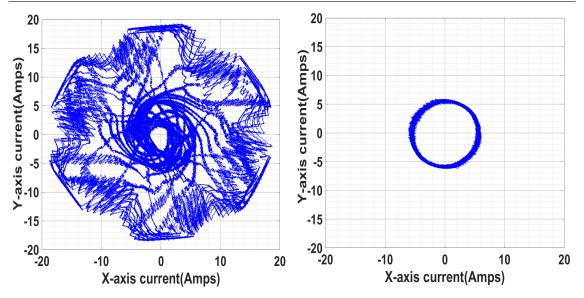

| 2.18 | The grid injected current space plot (X-Y plot) in weak grid scenario               |    |

|      | without (left) and with (right) PI controller gain compensation                     | 28 |

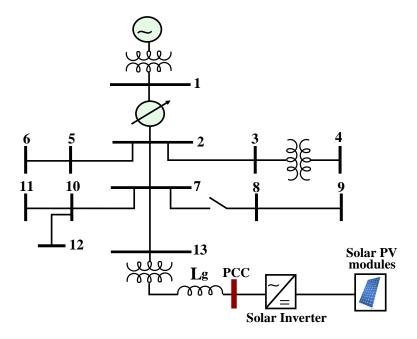

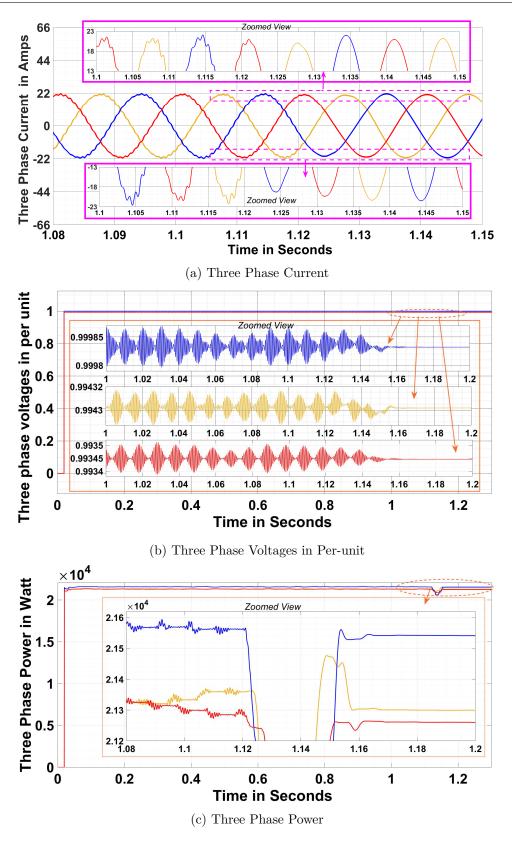

| 2.19 | The single line diagram of standard IEEE-13 bus system with solar inverter          |    |

|      | integrated at node 13                                                               | 28 |

| 2.20 | The solar inverter injection parameters at PCC considering the grid<br>inductance $L_g = 14$ mH without and with proposed controller gain                                                                                                                                                                                                                        |            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | characterization                                                                                                                                                                                                                                                                                                                                                 | 29         |

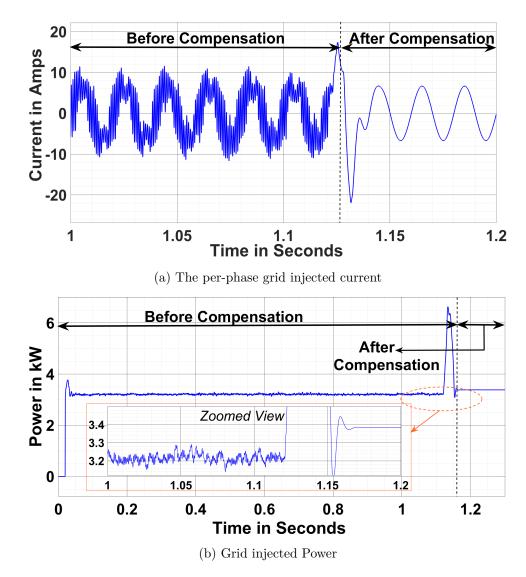

| 2.21 | Three Phase Current, voltages and power at node 13                                                                                                                                                                                                                                                                                                               | 30         |

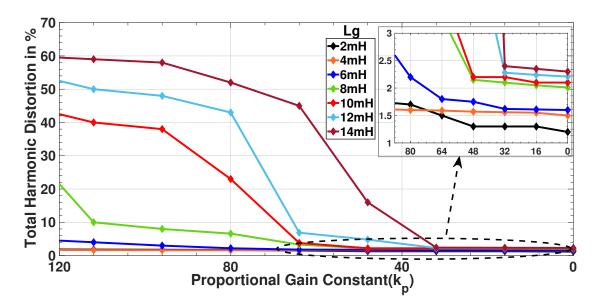

| 2.22 | The grid injected current %THD variations with varying grid inductance( $L_g$ ) and controller gain $K_p$                                                                                                                                                                                                                                                        | 31         |

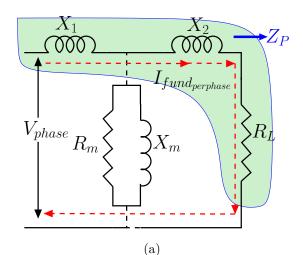

| 3.1  | Proposed series inverter topology with closed-loop current controller                                                                                                                                                                                                                                                                                            | 33         |

| 3.2  | (a) Equivalent per phase impedance of the plant referring onto the primary<br>of the transformer (b) The equivalent power circuit with per phase<br>equivalent impedance                                                                                                                                                                                         | 34         |

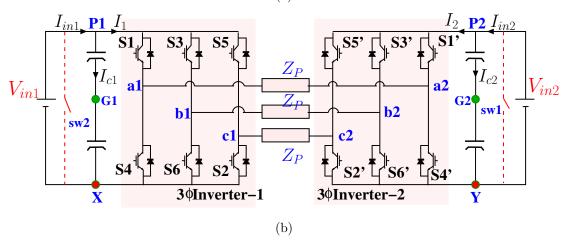

| 3.3  | (a) Space vector locations of Inverter-1 and Inverter-2 (b) The resultant load space locations of parallel inverter configuration, complementary switching and per phase balanced switching algorithm                                                                                                                                                            | 35         |

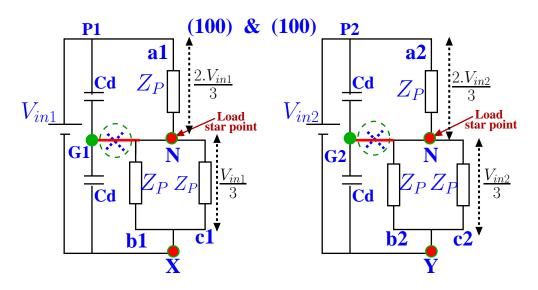

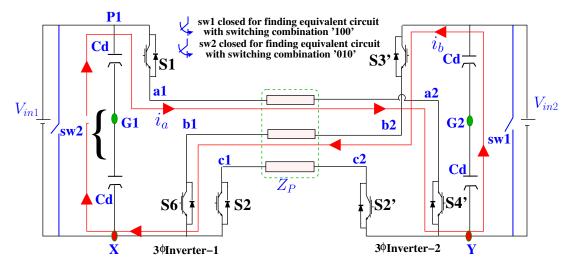

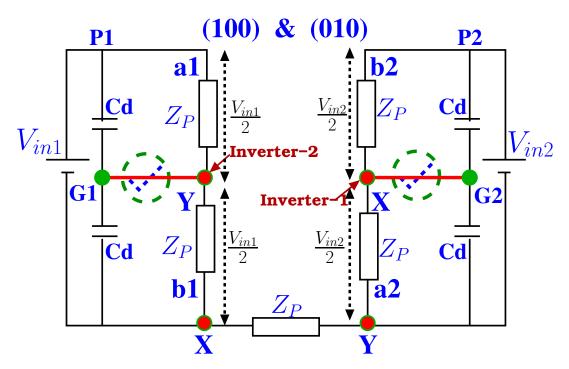

| 3.4  | The equivalent circuit diagram of parallel inverter with switching state 100 (Inverter-1) and 100 (Inverter-2) to compute CMV                                                                                                                                                                                                                                    | 36         |

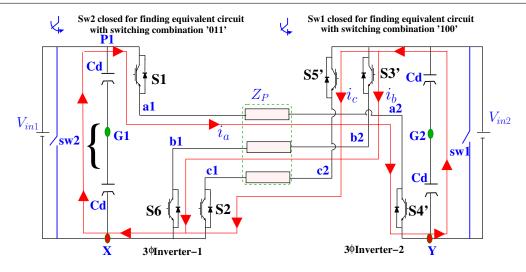

| 3.5  | The operational state of proposed configuration with switching state $14'$                                                                                                                                                                                                                                                                                       | 38         |

| 3.6  | The equivalent circuit of proposed configuration with switching state 1 '100' (Inverter-1) and 4' '011' (inverter-2) to compute CMV                                                                                                                                                                                                                              | 38         |

| 3.7  | The load current and the circulating current path of the proposed converter with switching state 14'                                                                                                                                                                                                                                                             | 39         |

| 3.8  | The operational state of proposed configuration with switching state $13^{\circ}$ .                                                                                                                                                                                                                                                                              | 40         |

| 3.9  | The equivalent circuit of proposed configuration with switching state 1 '100' (Inverter-1) and 3' '010' (inverter-2) to compute CMV                                                                                                                                                                                                                              | 40         |

| 3.10 | The load current and the circulating current path of the proposed converter with switching state 14'                                                                                                                                                                                                                                                             | 41         |

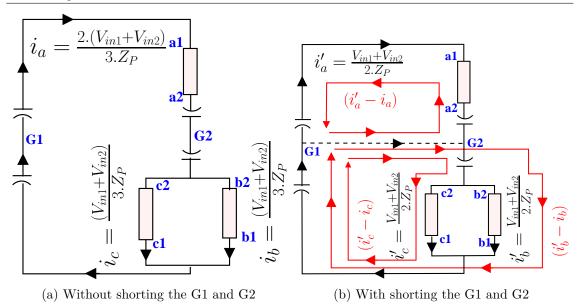

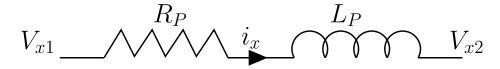

| 3.11 | Simplified per phase impedance of the plant                                                                                                                                                                                                                                                                                                                      | 41         |

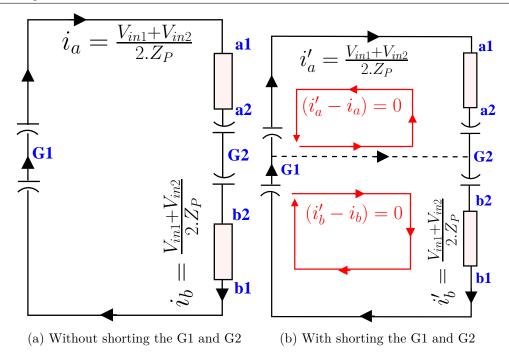

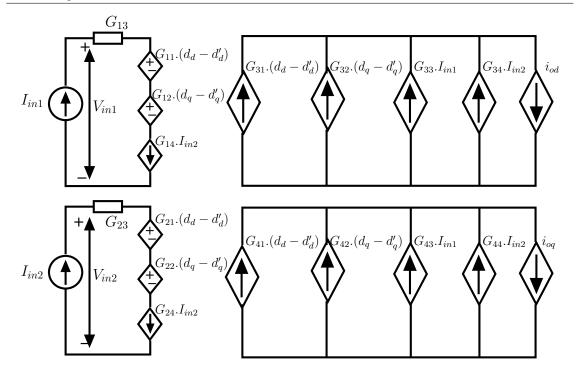

|      | Dynamic network model of proposed configuration derived from state space<br>model                                                                                                                                                                                                                                                                                | 45         |

| 3.13 | Small signal model of inverter to design the controller in dq-domain                                                                                                                                                                                                                                                                                             | 45         |

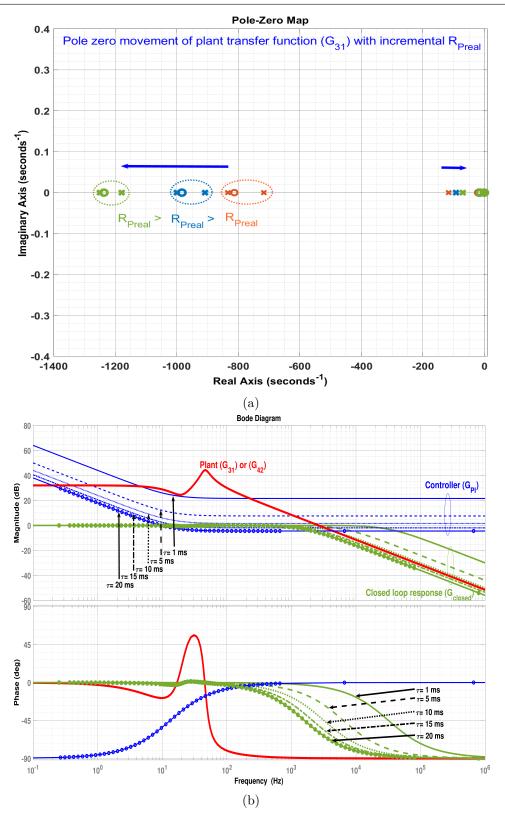

| 3.14 | (a) The pole zero location of the plant $G_{31}$ with varying load $R_P$ (b)<br>Frequency response of the plant, controller and closed-loop response of the<br>proposed configuration with varying $\tau$                                                                                                                                                        | 46         |

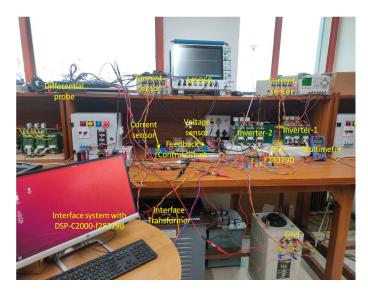

| 3.15 | Lab hardware prototype of proposed configuration                                                                                                                                                                                                                                                                                                                 | 47         |

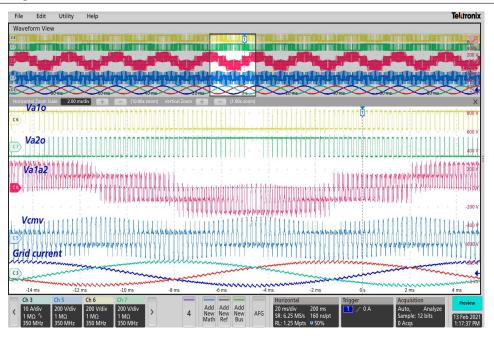

|      | Inverter-1 a-phase pole voltage $(1^{st} \text{ trace})$ , inverter-2 a-phase pole voltage $(2^{nd} \text{ trace})$ , a-phase voltage across the primary of the transformer $(3^{rd} \text{ trace})$ , CMV between the mid point of the capacitor $(4^{th} \text{ trace})$ and abc- phase primary current (bottom trace) for complementary switching algorithm . | 49         |

|      | primary current (bottom trace) for complementary switching algorithm                                                                                                                                                                                                                                                                                             | <b>4</b> 9 |

| 3.17 | Inverter-1 a-phase pole voltage $(1^{st} \text{ trace})$ , inverter-2 a-phase pole voltage |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | $(2^{nd} \text{ trace})$ ,a-phase voltage across the primary of the transformer $(3^{rd})$ |    |

|      | trace), CMV between the mid point of the capacitor $(4^{th} \text{ trace})$ and abc-       |    |

|      | phase primary current (bottom trace) for Per Phase Balanced switching                      |    |

|      | Methodology                                                                                | 49 |

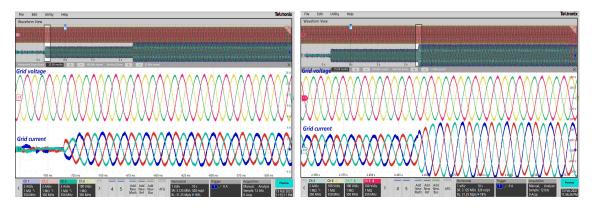

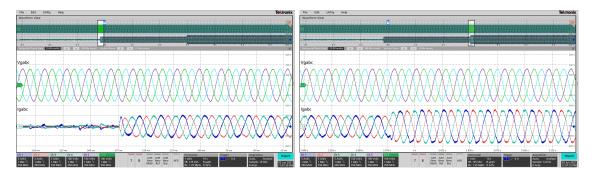

| 3.18 | Three phase grid voltage( $V_{abc}$ )(unit x-axis: 25ms/div; y-axis: 100 volts/div)        |    |

|      | and grid injected current $(I_{abc})$ (unit x-axis:25ms/div; y-axis: 2 Amps/div)           |    |

|      | with step change in $i_{dref}$ from 0 to 0.6PU (left trace) and 0.6PU to 1 PU              |    |

|      | (right trace) considering $\tau = 60$ ms and corresponding $K_P = 0.1$ and $K_I =$         |    |

|      | 1000)                                                                                      | 50 |

| 3.19 | Three phase grid voltage<br>( $V_{abc}$ (unit x-axis: 25ms/div; y-axis: 100 volts/div)     |    |

|      | and grid injected current<br>( $I_{abc}$ )(unit x-axis: 25ms/div; y-axis: 2 Amps/div)      |    |

|      | with step change in $i_{dref}$ from 0 to 0.6PU (left trace) and 0.6PU to 1 PU              |    |

|      | (right trace) considering $\tau = 5$ ms and corresponding $K_P = 1.2$ and $K_I =$          |    |

|      | 12000)                                                                                     | 50 |

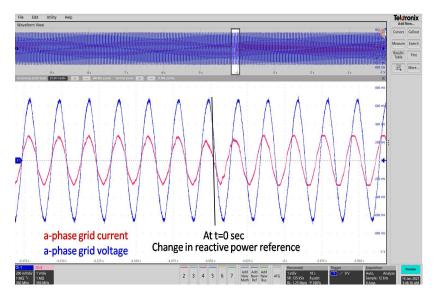

| 3.20 | a-phase Grid voltage $(V_{abc})$ (unit x-axis: 5ms/div; y-axis: 60 V/div) and              |    |

|      | a-phase grid injected current $(I_{abc})$ (unit x-axis: 25ms/div; y-axis: 4                |    |

|      | Amps/div) with step change in reactive power reference from 0 to 0.2PU .                   | 51 |

|      |                                                                                            |    |

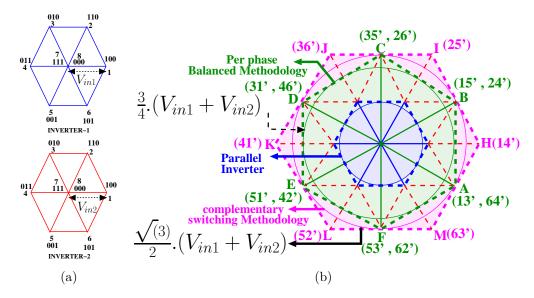

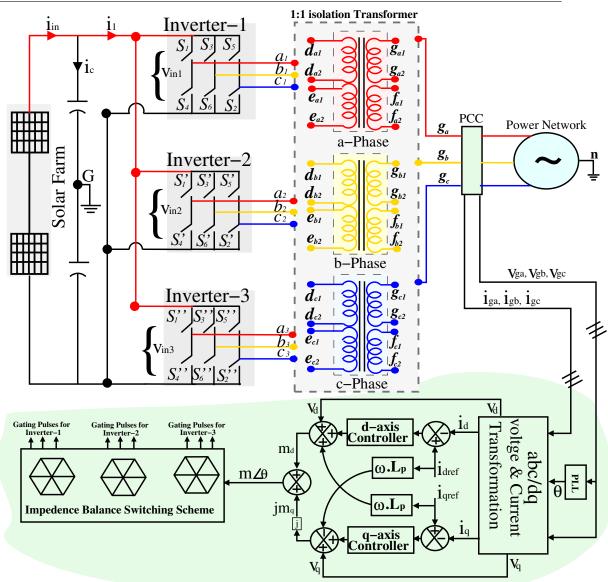

| 4.1  | The circuit diagram of proposed high voltage gain solar inverter                           | 54 |

| 4.2  | The a-phase primary and secondary side interface transformer connections                   |    |

|      | to illustrate proposed variants                                                            | 56 |

| 4.3  | The equivalent circuit realization by transforming grid impedance onto the                 |    |

|      | primary of the transformer                                                                 | 57 |

| 4.4  | The equivalent transformed impedance circuit with switching state 1 3' 5"                  |    |

|      | and corresponding current path for variant-1 & 2 $\hdots$                                  | 58 |

| 4.5  | The equivalent per phase impedance circuit with applied superposition                      |    |

|      | principle on proposed configuration by keeping inverter-1 (left),                          |    |

|      | inverter-2(middle) and inverter-3 (right) with switching state $13'5"$ for                 |    |

|      | variant-1 and variant-2                                                                    | 58 |

| 4.6  | The space vector realization with demonstrated switching state $\ . \ . \ . \ .$           | 60 |

| 4.7  | The equivalent transformed impedance circuit with switching state 1 3' 3"                  |    |

|      | and corresponding current path for variant-3                                               | 61 |

| 4.8  | The equivalent per phase impedance circuit with applied superposition                      |    |

|      | principle on proposed configuration by keeping inverter-1 (left),                          |    |

|      | inverter-2(middle) and inverter-3 (right) with switching state 13'3" for                   |    |

|      | variant-3                                                                                  | 61 |

| 4.9  | The space vector locations to realize the grid space vector correspond to                  |    |

|      | per-phase impedance balance                                                                | 62 |

| 4.10 | Small signal flow diagram of proposed configuration in dq-domain                           |    |

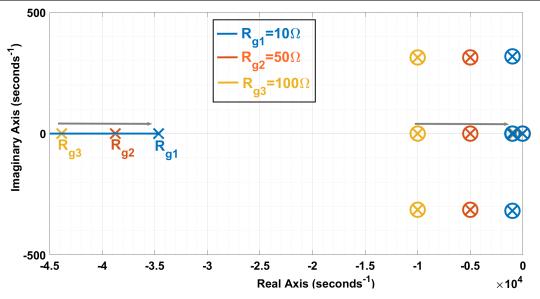

|      | The closed loop Pole-Zero distribution with varying load $R_q$ and chosen $K_p$            |    |

|      | and $K_i$ for desired system response                                                      | 68 |

|      |                                                                                            |    |

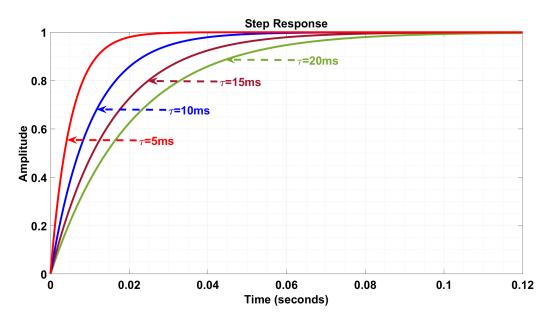

| 4.12 | The Step response of closed loop system at different time $constant(\tau)$ with             |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | adjusted controller gains $K_p$ and $K_i$                                                   | 68 |

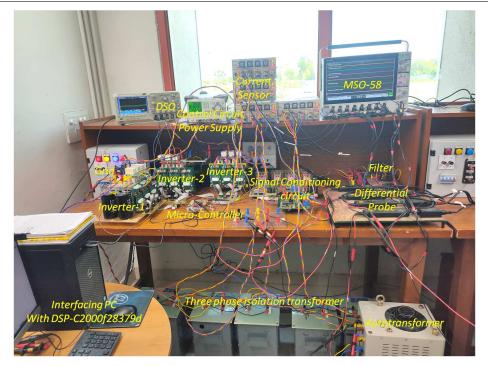

| 4.13 | Lab-hardware set-up of proposed configuration                                               | 69 |

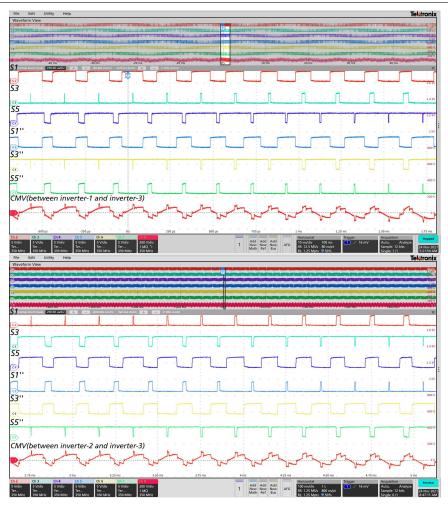

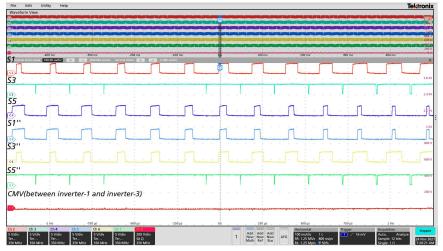

| 4.14 | The top six traces represents switching pulses of inverters (X-axis :                       |    |

|      | $0.25 \mathrm{mS/div}$ and Y-axis: $5 \mathrm{V/div}$ ) and the bottom trace represents the |    |

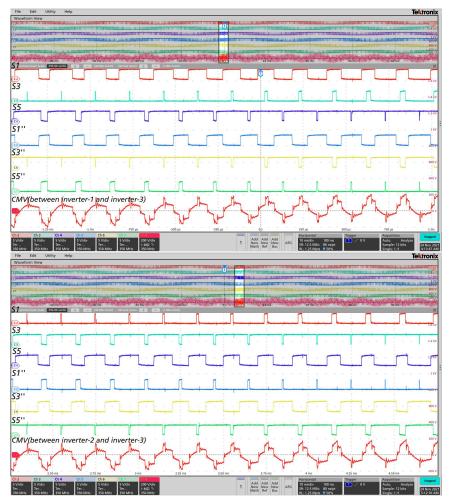

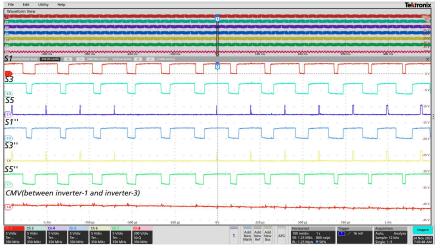

|      | common mode voltage (X-axis: $0.25$ ms/ div and Y-axis: $200$ V/div) of Variant-1           | 70 |

| 4.15 | The top six traces represents switching pulses of inverters (X-axis : $0.25 \text{mS}/$     |    |

|      | div and Y-axis: $5V/div$ ) and the bottom trace represents the common mode                  |    |

|      | voltage (X-axis:0.25ms/div and Y-axis:200V/div) of variant-3                                | 71 |

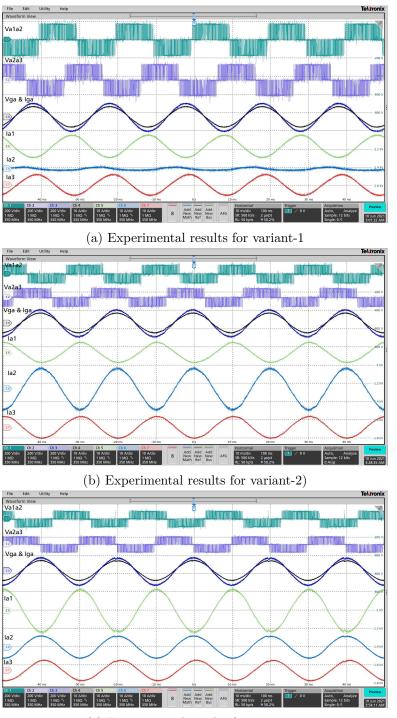

| 4.16 | The transformer primary Winding-1 a-phase voltage $(V_{a_1a_2})(1^{st}$ trace, unit         |    |

|      | x-axis: 10 ms/div; y-axis: 200 volts/div), Primary winding-2 a- phase                       |    |

|      | voltage $(V_{a_2a_3})(2^{nd}$ trace ,unit x-axis: 10 ms/div; y-axis: 200 volts/div),        |    |

|      | a-phase grid voltage(unit x-axis: 10 ms/div; y-axis: 200 volts/div) and grid                |    |

|      | injected current(unit x-axis: 10 ms/div; y-axis: 10 Amps/div) $(3^{rd} \text{ trace})$ ,    |    |

|      | a-phase primary current of inverter-1 ( $4^{th}$ ), inverter-2 ( $5^{th}$ trace) and        |    |

|      | inverter-3 (bottom trace,<br>unit x-axis: 10 ms/div; y-axis: 10 Amps/div) of                |    |

|      | proposed configuration                                                                      | 72 |

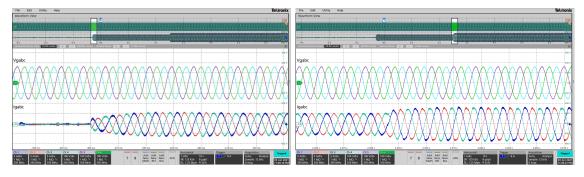

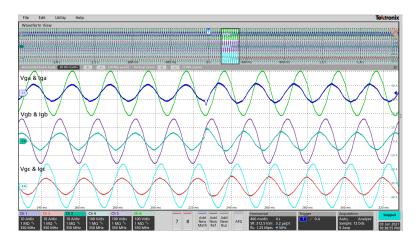

| 4.17 | Three phase grid voltage $(V_{g_{abc}})$ (top trace, unit x-axis: 25 ms/div; y-axis:        |    |

|      | 100 volts/div) and grid injected current ( $I_{g_{abc}}$ ) (bottom trace, unit x-axis:      |    |

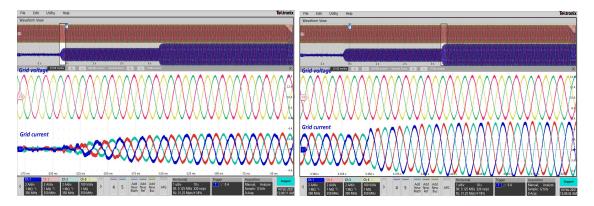

|      | 25 ms/div;y-axis:5 Amps/div) with step change in $i_{dref}$ from 0 to 0.4PU                 |    |

|      | (left trace) and 0.4 PU to 0.6 PU (right trace) with $K_p=0.0957$ and $K_i=259$             | 74 |

| 4.18 | Three phase grid voltage $(V_{g_{abc}}$ ) (top trace, unit x-axis: 25 ms/div; y-axis:       |    |

|      | 100 volts/div) and grid injected current ( $I_{g_{abc}}$ ) (bottom trace, unit x-axis:      |    |

|      | 25 ms/div; y-axis:5 Amps/div) with step change in $i_{dref}$ from 0 to 0.4PU                |    |

|      | (left trace) and 0.4PU to 0.6 PU (right trace) with $K_p = 0.4$ and $K_i = 1034$            | 74 |

| 4.19 | Three Phase grid voltage ( $V_{g_{abc}}$ , unit x-axis: 20 ms/div; y-axis: 100 V/div)       |    |

|      | superimposed on three phase grid injected current<br>( $I_{g_{abc}}$ ;unit x-axis: 20       |    |

|      | ms/div; y-axis: 10 Amps/div) with step change in reactive power reference                   |    |

|      | from 0 to 0.2 PU at t=225 ms                                                                | 74 |

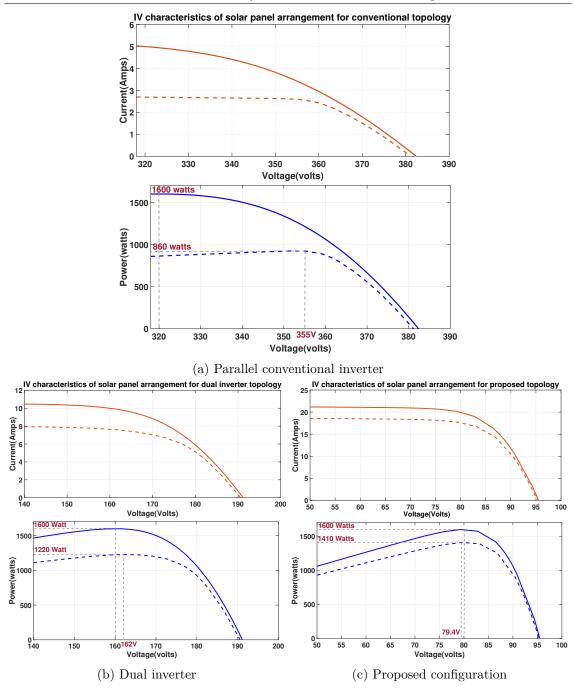

| 4.20 | IV (left) and PV (right) characteristics of solar panel arrangement during                  |    |

|      | full (solid line) and partial (dotted line) irradiance conditions $\ldots$                  | 76 |

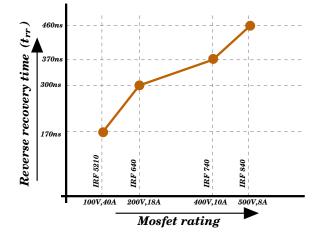

| 4.21 | Variation of reverse recovery time $(t_{rr})$ of IRF family switching devices               |    |

|      | reference to voltage blocking capability                                                    | 77 |

# List of Tables

| 2.1 | The operating parameters of the grid connected inverter $\ldots$                     | 23 |

|-----|--------------------------------------------------------------------------------------|----|

| 2.2 | The tested grid parameters with identified proportional gains $\ldots \ldots \ldots$ | 24 |

| 3.1 | The proposed solar inverter switching combinations, corresponding                    |    |

|     | resultant load space vector and CMV profile                                          | 37 |

| 3.2 | Experimental operating parameters of proposed series inverter                        | 48 |

| 4.1 | The proposed solar inverter switching combinations, corresponding                    |    |

|     | resultant load space vector and CMV profile for variant-1 and variant-2 $$           | 59 |

| 4.2 | The proposed solar inverter switching combinations, corresponding                    |    |

|     | resultant load space vector and CMV profile for variant-3 $\ldots$                   | 63 |

| 4.3 | Experimental operating parameters of proposed Configuration                          | 69 |

| 4.4 | Comparison of proposed variants                                                      | 73 |

| 4.5 | The performance comparison matrix between proposed topology and other                |    |

|     | conventional topologies                                                              | 77 |

| 4.6 | The energy yield performance comparison table during partial irradiance              |    |

|     | condition                                                                            | 77 |

# Chapter 1

# Introduction

### 1.1 Single Stage Grid Connected Inverter

In recent times, the single stage solar inverters as shown in are popular to interface solar farms with utility grid. The higher magnitude of energy generated by the solar farms can feed to the grid at defined frequency and voltage with different topology of three phase inverters [1]-[2]. The single-stage grid-connected solar inverters are responsible for tracking the solar farm's maximum power point (MPPT) and converting DC energy into AC at the grid frequency. In a grid-connected Inverter topology, the parallel operated modular single-stage conversion topologies are more popular because of the system capacity, modularity and efficiency. Since the DC-DC conversion stage is eliminated in the single stage conversion system, parallel connected inverter modules are fed from the same DC bus. In this configuration, it is essential to derive higher DC potential compare to conventional two stage conversion system to synthesizes the grid voltage. The higher DC potentials are synthesized in a solar farm by connecting number of solar panels in series. In high wattage solar farms, the higher DC bus potentials demand high voltage rating switching devices and DC capacitors and add substantial stress on inverter components. Since the power electronic switches and DC capacitors defines the reliability and cost of the overall system, it is necessary to protect from excess DC potentials to improve the reliability of the inverter modules. Apart from this, the importance of system impedance integrity for efficient solar energy harvesting, emphasizes the role of interface converters in stabilizing the system impedance accordance with the source and power network characteristics. The impedance arbitration conventionally achieved through interface inverter by adjusting the control parameters in accordance with the injected current patterns [3]-[4]. The limitations with the control parameters demands system stability analysis for wide range of operations. The improper arbitration of impedance due to restrictions with the control parameters invoke power oscillation at PCC, subsequently drag the system to unstable region[5]-[6]. Therefore the issues associated with solar interfaced grid connected inverter

- 1. Power quality issues in the weak grid scenario due to uncompensated grid inductance after the point of common coupling (PCC).

- 2. Elevated DC bus potential and its grounding

- 3. Inter and intra Circulating currents within the inverter modules.

need to be resolved to inject smooth grid power.

#### 1.1.1 Power Quality Issues in Weak Grid Coupled Solar Inverter

In a weak grid scenario, the additional grid impedance further deteriorates stability margins due to offered negative damping to frequencies vicinity to synchronous frequency arises as a consequence of complex interactions between the system control parameters and network impedance [7]-[8]. The frequency oscillations at the PCC distort the reference to the inverter taken through PLL. In general, the synchronous reference frame based PLLs are more popularly used for generating robust reference by shaping the dq-impedance of the inverter[9]. In the past, the researchers have explored PLL dynamics under weak grid scenario along with the control parameters<sup>[10]-[11]</sup>. Based on the past study, it has been identified that the PLL would bring the negative resistance in the sub synchronous frequency band under weak grid scenario further worsen the stability margins of the system. The influential negative resistance mechanism introduced by the PLL on the system instability is presented comprehensively in [12]-[11]. Further, the self-synchronous phenomenon of grid impedance impact on system stability margins is studied by introducing the non linear PLL model<sup>[13]</sup>. However, the increased complexity of the current controller with non linear models forced the researchers to reconsider linear PLL models only, reiterated the negative resistance due to reshaping of inverter dq-axis impedance. To overcome the negative resistance at sub-synchronous frequencies, the researchers have introduced the band pass filters to compensate the negative effect with compromised bandwidth[14]. The limited bandwidth of the PLL restrict the current controller significance in dynamic reference tracking and noise rejection. The dynamic response further compromised with defined stability margins of current controller due to cascaded effect [15] & [16]. In [16], the method of introducing the PLL dynamics into the current controller is demonstrated to avoid undesirable interactions of the PLL with the current controller. The additional phase shift with introduced filters in PLL deteriorate the control dynamics of the overall system. The deteriorated dynamic response and additional phase shift significantly impact the system during fault ride through conditions [17]. Considering the trade off with PLL impedance shaping and dynamic response, the researchers have investigated various control methodologies including outer voltage loop control addition [18]-[19], ac-bus voltage controller[20], impedance phase compensation [21] etc without disturbing the PLL gain. These methods are mainly designed to address the frequency oscillations at PCC demanded additional control loops and complex algorithms to address the stability margin, diminishes the role of current controller significantly. Since the current controller parameters effect on the stability margins are not established completely yet, the external loop shaping methods along with the current controller gain compensation got prominence. It is mainly due to unexplored system impedance interaction model that mimicks the actual behaviour of the system under weak grid scenario. But with the accurate system model, external loop shaping methods can be eliminated completely. In this direction, attempts are made to study the system model in weak grid scenario through state space and nyquist impedance based modeling, but with limited parameters<sup>[22]</sup>. Further, impedance based models are studied using lumped equivalent circuit to analyse the system stability but the influence of control and circuit parameters are neglected. In [23], a simplified model for the plant or the controller is presented but it makes the system stability analysis cumbersome while realizing the effect of simultaneous variations in the control and plant parameters. In [24], researchers have modelled the interface converter based on positive and negative sequence impedance directly in phase domain and studied independently for stability analysis under single-input single-output system. But this method is not appropriate for wide range grid inductance variations. In literature [22]-[24] it has been identified that the system stability not necessary improved with reduced grid inductance but influenced by both X/R ratio and the grid inductance. The established works so far, described the 'R' with reference to network line resistance. But not explored the influence with reference to grid power injection resistance  $(V_q/i_q)$ . Further, in the literature it has been identified that the inductance of either side of feedback point influences the system stability but the effect of power injection resistance is not considered to evaluate the stability margins. The work reported in this paper, built around deriving the positive damping for the PCC oscillations through a thorough assessment of system natural response in weak grid scenario. The natural response of the system is influenced by control parameters, impedance of system and their interactions. In stiff grid scenario, the system impedance are compensated to model the controller gains for desired injected power characteristic. Whereas in weak grid scenario, the influence of network impedance need to be assessed in the presence of system impedance to model the controller gains. The interaction between the system impedance (filter inductance and grid injected power resistance), network impedance (grid inductance) and controller gains requires multi dimensional assessment forced past researcher to derive the simplified models. Since the derived existing models are not exactly mimicking the weak grid scenario, it is required to use a secondary controls (PLL shaping, feed-forward damping, additional hardware etc) along with the current controller gain compensation for grid injected current quality shaping [7]-[25]. But with appropriate modeling of weak grid scenario, the current controller gain compensation is sufficient to bring the positive damping to power oscillations at PCC.

#### 1.1.2 Elevated DC Bus Potential and Circulating Current Issues

At present, modular inverters are dominating in the solar interface inverter portfolio, mostly parallel configurations. The modular single-stage parallel inverter is well known for sharing power in terms of current. In a parallel configuration, the DC bus voltage requirement to synthesize the desired AC voltage demanded to connect with utility grid is high, typically 1000 V [26]. Along with elevated DC bus voltages, the parallel inverters are also suffering from the need for operating DC bus in floating condition due to CMV present in the inverter circuit. In parallel inverter topology, all modular inverters are assumed to be identical characteristic impedance and operate with the same switching instances to connect all inverter modules to the same DC bus. But it is improbable that the modular inverters operating in parallel configuration have an identical characteristic impedance resulting in circulating current [27]-[28] within the inverter modules due to CMV. In parallel configurations, the circulating currents are classified as intra-modular (within the inverter modules) and the inter network (DC-AC) circulating currents. The intra-modular circulating currents result from instantaneous voltage between the AC network (load star-point) and the DC reference point that appear due to instantaneous impedance mismatch. The researchers have identified the impedance mismatch in parallel configuration mainly due to control signal propagation delays and maximum power point impedance variations correspond to solar irradiance. Since the circulating currents affects the grid injected power quality, the researchers have investigated various methods including augmented impedance in zero sequence path and customized control technique to reduce the circulating current. Many researchers have attempted to suppress the circulating current through isolation, introducing a high impedance path in the circuit, and synchronized control in the recent past. In isolation method [29]-[30], the DC bus is isolated from AC bus through a three-phase transformer but increases the system's size and cost. Further researchers have tried to introduce a high impedance path in the circuit through coupled inductor [31]-[32] to reduce the circulating current. Achieved a high impedance path through a coupled inductor can restrict high frequency circulating currents effectively. Whereas the suppression of low-frequency component can be achieved by different control and modulation techniques like a hybrid or modified space vector PWM [33]-[34], selective harmonic PWM [35], multi-carrier PWM method [36]-[37]. To reduce the circulating current provoked due to switching delays, the past researchers have proposed various synchronized control approaches like PI controller for master-slave configuration [38], decentralized controllers, Deadbeat control [39]-[40], zero vector feedforward control [41]. The synchronized approach treats all modular inverters as a single inverter and control all modular units through high frequency bandwidth communication link to achieve the synchronized switching [38]-[41]. The attempts made so far to reduce the circulating currents demands either extra hardware circuitry or complex control algorithm, despite complete elimination of circulating current is not possible. Apart from the intra-modular circulating currents, the inter network circulating current arises mainly due to adopted grounding methods with AC and DC networks. In any distribution power network, the star point of the AC three phase winding is connected to ground to derive the neutral wire of the power network. With grounded AC network, the DC of the interface inverters need to be isolated from the ground to avoid the virtual zero sequence current path between AC and DC networks in case of transformer less configuration. Otherwise galvanic isolation need to be maintained between AC and DC network through transformer to suppress the zero sequence current path. Even with the transformer, the solid DC bus grounding is not advisable considering the circulating currents between the inverter modules and the ground resistivity between AC and DC network. Therefore the industries are preferring either impedance grounding or reducing the the voltage magnitudes correspond to the circulating currents through devoted inverter topologies. Although the impedance grounding address the safety requirements partially, but considering the reliability of the system, the solid DC grounding is recommended by eliminating circulating currents.

Apart from the instantaneous impedance of the circuit, the DC bus potentials also influences the magnitudes of the circulating current [42]-[43]. The elevated DC bus potentials in the single stage parallel inverter topologies not only deteriorates the performance of the inverter modules but also aggravate the reliability issues of the solar panels due to potential induced degradation (PID) effect [44]-[45]. In a parallel inverter, the DC potentials generated through series solar strings with grounded frames experience a significant voltage buildup across each solar cell. Depending upon the potential buildup across the cell, the leakage current flowing through grounded frames damages the solar cell, overall, affects the reliability of the solar panels. As per the available literature, the PID effect can be minimized by reducing the DC potentials or with appropriate grounding of DC bus [44]. In solar inverters, various methods of DC bus grounding are proposed through cascaded boundary dead beat control [46], isolated AC-DC conversion unit with specialized control unit [45], and zero sequence damping [47]. So far, the proposed methods required extra hardware circuitry to mimic the virtual grounding across the DC bus of the solar inverter. Apart from this, the past study shows that the DC bus's potentials affect the performance of the DC capacitors and the semiconductor switches. To reduce the DC voltage and common mode stress on the DC capacitors/switches, researchers have proposed various methods, including Multilevel inverter [48], current source inverters [49], etc. Owing these issues, the researchers have studied the series injection topologies based on the dual inverter configuration as a grid interface inverters for adopting unique feature of deriving the AC voltage with reduced DC bus potential [50]-[51]. In the motor drive applications, the researchers have concentrated on addressing the motor applications' issues like minimization of bearing current [52], improving motor torque ripple performance [53], etc. In motor applications, the neutral point of the load is floating. In the power network case, the neutral point of the load needs to be grounded, making the circulating current analysis different from the motor applications. Besides, the existing CMV and neutral grounding demand the solar inverter to operate with a floating DC bus that affects the life of solar panels and inverter. Overall, the higher DC bus voltage and the CMV degrade the performance of modular solar interface converters. Although with dual inverter configurations, the voltage responsible for the circulating current can be reduced along with DC bus voltage, but the impedance imbalance arises due to asynchronous switching may worsen the frequency of the circulating current. But the offered degree of freedom with redundant switching states in series injection configurations ensures the desired characteristic realization. In literature, the selection of switching states for dual inverter to realize the grid voltage is demonstrated through coordinated closed loop control [54], sliding mode control [55] etc. Although with the appropriate switching state selection, the series injection with dual inverter requires only half of the DC bus voltage compare to parallel inverter topology to generate the grid voltage, but suffer from the circulating current within the inverter module demands isolated DC bus for both the inverter [56]. The circulating currents are mainly due to the resultant voltage between the DC capacitor midpoint and the ground restricting the DC bus grounding. In a dual inverter configuration, the instantaneous voltage between the two inverter's DC negative bus, known as common-mode voltages (CMV), forces the circulating current within the circuit when two inverters connect with the common DC bus. The instantaneous circulating currents are the consequence of CMV arises due to three-phase inverter switching, enforce the zero-sequence harmonic currents circulates within the two inverters in a series inverter configurations. These circulating harmonic currents create a thermal runaway issue in semiconductor switches and the transformer connected for voltage sharing that negatively influences the long-term reliability of the inverter circuit. Considering thermal runaway issues, it is recommended to eliminate the circulating current or use the isolated DC bus for the individual inverter. But, in case of the dual-inverter configuration with isolated DC bus is inefficient due to poor yielding of energy at partial irradiance condition and demands the coordinated control algorithm to access the maximum power across the inverters. To address the problems associated with isolated DC bus, the recent work reported in [56]- [57] demonstrated the selection of switching states of dual inverter to cancel the instantaneous circulating current to employ the common DC bus for both the inverters present in series injection topology but with reduced voltage gain. The concept of instantaneous impedance balance can be further explored to realize the high gain voltage topologies considering the associated technological features like

- Reduced demanded DC potential to realize the grid voltages: Improve the power efficiency of the interface inverter, improve the solar inverter module reliability[58].

- Operate with common DC bus: provide the ease in control to balance the extracted power for wide range of irradiance [56] [57].

- Provision of DC bus solid grounding : Improve the reliability of the solar panels through reduced PID effect & ensure the strict compliance with safety standards [59]-[60].

### 1.2 Motivation

#### 1.2.1 Year-Wise Installed Capacity of Energy Generation in India

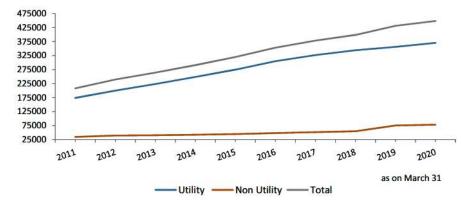

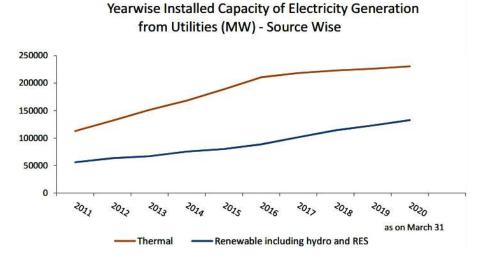

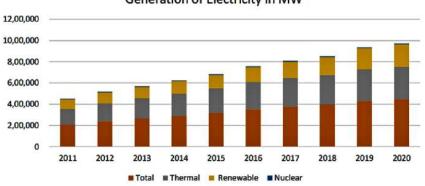

As it is shown in Fig.1.1a [61], India's energy requirement is steeply rising from 2011 to 2020. Whereas in generation, the thermal generation captures the maximum share from 2011 to 2020, but the thermal generation curve gets flattened from 2016 to 2020 due to increased generation through renewable sources as it is visible from Fig.1.1b. From Fig.1.2a and Fig.1.2b, it is evident that nation is moving toward renewable energy generation, and the preferably towards the solar due to its abundance and cleanness. On the other hand, Government of India has launched many initiatives to promote clean energy generation, as listed in sub-section 1.2.2 [62].

Yearwise Installed Capacity of Electricity Generation (MW) from utilities and non utilities

(a) Year-wise installed capacity of electricity generation in MW (X-axis: Year; Y-axis: Electricity generation in MW)

(b) Year-wise and source-wise installed capacity of electricity generation in MW (X-axis: Year; Y-axis: Electricity generation in MW)

Figure 1.1: Installed capacity of electricity generation in MW

#### 1.2.2 Government Initiatives to Promote Clean Energy Generation

- 1. Pradhan Mantri kisan Urja Suraksha evam Utthaan Mahabhiyan (PM-KUSUM) scheme for solar pumps where government of India (GoI) has targeted to setup 10,000 MW of decentralized Grid Connected Renewable Energy Power Plants on barren land. GoI planned to install 17.50 Lakh stand-alone solar agriculture pumps and solarisation of 10 Lakh agricultural pumps connected with the grid.

- 2. Ude Desh ka Aam Nagarik (UDAN) scheme for Airport runway lighting system, Solar integrated technologies for railways and Battery charging station.

- 3. Deen Dayal Upadhyaya Gram Jyoti Yojana (DDUGJY) for Rural electrification and providing Micro-grid solutions to rural and hilly areas.

- 4. FAME(Faster Adoption and Manufacturing of Electric Vehicles) to give the boost

Yearwise and sourcewise Installed Capacity of Generation of Electricity in MW

(a) Year-wise and source-wise installed capacity of electricity generation in MW (X-axis: Year ; Y-axis: Electricity generation in MW)

(b) Cumulative installed capacity of grid interactive renewable power by type (in MW) (X-axis: Year ; Y-axis: Electricity generation in MW )

Figure 1.2: Cumulative installed capacity of grid interactive renewable power by type (in MW) (X-axis: Renewable sources ; Y-axis: Energy generation in MW)

towards the faster development and adaptation of electric vehicles in India.

The future needs and criticality of renewable energy adaptation in the generation are the primary motivation behind this work to carry in the field of solar energy generation and integration with the grid.

### 1.3 Objectives

- 1. A current controller gain characterization of weak grid coupled solar inverter through impedance interaction modeling

- 2. To reduce the DC bus potential of the single-stage grid-connected inverter and provides the flexibility of DC bus grounding

- 3. To eliminate the circulating current within the inverter modules in a single-stage

grid-connected inverter through a novel high gain series inverter with asynchronous switching.

### **1.4** Organization of the thesis

- 1. Chapter 1 deals with an introduction revolving around the power quality issues associated with single-stage grid-connected inverters due to improper arbitration of impedance in weak grid scenarios, elevated DC bus potential, and circulating current within the inverter modules. Later, the Motivation and objectives of the thesis are also furnished along with the organization of the thesis.

- 2. Chapter 2 deals around deriving the positive damping for the PCC oscillations through a thorough assessment of system's natural response in a weak grid scenario. The presented work also attempted to derive the equivalent system impedance model by observing the natural interactions between the system and network impedance in the synchronous reference frame. With the obtained natural response through the axis transformation principle, the current controller gain characterization is proposed to accomplish the positive damping for power oscillations at PCC by assessing the controller sampling time effect. The presented work also briefed about accomplishing the grid injected power quality as per IEEE-1547(IEEE-519) standards by tuning of the positive damping towards the natural frequency of identified equivalent system impedance model.

- 3. Chapter 3 discusses the new series inverter topology for the single-stage grid-connected inverter. The proposed topology eases the stress on the dc bus and protects the solar inverter from the issues associated with elevated dc potential (potential induced degradation effect, switch operating voltage stress, etc.), DC bus grounding, and circulating current within the inverter modules. The proposed configuration eliminates the common mode voltage (CMV) which is responsible for the circulating current by choosing the two inverters' appropriate switching combinations.

- 4. Chapter 4 deals with the high gain voltage solar interface inverter topology aiming to reduce the DC bus voltage requirement further compare to the dual inverter series topology to realize the grid voltage. The grid voltage realization and the corresponding DC bus requirement are demonstrated through three variants of the proposed topology. For all three variants, the independent switching schemes are devised to accomplish the instantaneous per-phase impedance balance while synthesizing the grid voltage. With the devised switching schemes, all proposed variants operate with a common DC bus. Further, the closed-loop controller modeling is demonstrated for the proposed configuration through state space analysis for stable operation at the desired dynamic response.

- 5. Chapter 5 presents the conclusion and future scope of the research work.

# Chapter 2

# A Current Controller Gain Characterization of Weak Grid Coupled Solar Inverter Through Impedance Interaction Modeling

### 2.1 Single stage grid connected solar inverter configuration

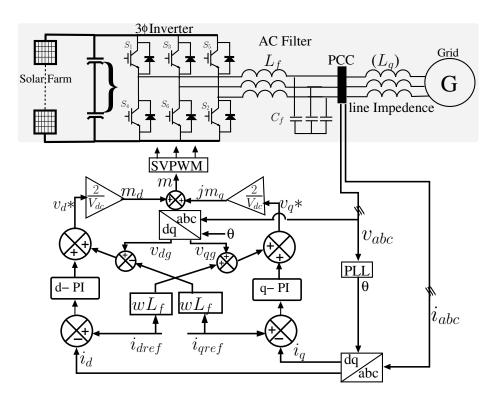

The space vector pulse width modulated (SVPWM) grid connected solar inverter with closed loop control is shown in Fig.2.1. In SVPWM, the DC bus utilization is more compare

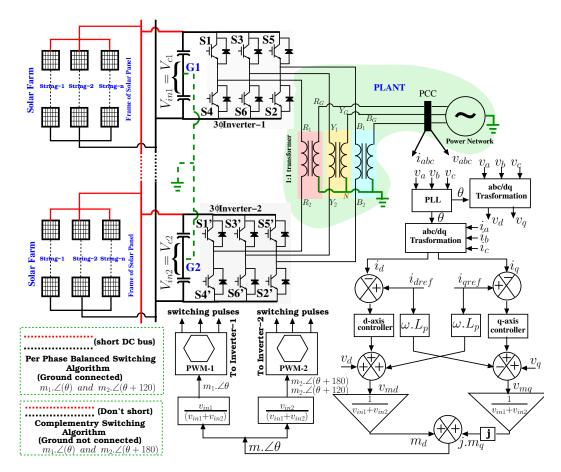

Figure 2.1: The circuit diagram of single stage grid connected inverter

to other PWM techniques including continuous and discontinuous PWMs. With SVPWM the DC bus utilization is approximately 16% more compare to Sine PWMs technique. In the closed loop control, the grid condition assessed by sensing the three phase voltages  $(v_a, v_b, v_c)$  and currents  $(i_a, i_b, i_c)$  at the PCC. The three phase voltages sensed at PCC are passed to the PLL to generate the reference angle  $\theta$  for the interface inverter. The reference angle  $\theta$  is used to convert the three phase voltages and current on stationary reference frame into two phase synchronous reference (dq) frame. On the translated dq reference frame with grid voltage frequency  $(\omega)$ ,  $v_{qg}$  is zero and  $v_{dg}$  appear to be the DC quantity correspond to the magnitude of the three phase grid voltages. Thus  $v_{dq}$  act as reference for the current control loop align in phase with d-axis shown in Fig.2.2. The q-axis is the orthogonal to d-axis represents the reactive power requirement of the system. In the stiff grid scenario the filter inductance  $L_f$  is the only inductance connected between the PCC and Inverter. So in order to deliver the desired active power as shown in Fig.2.2 to the grid, the reactive power compensation correspond to filter inductance  $L_f$  is given in the feed forward q-current loop shown in Fig.2.1. The current controller generate the corresponding modulation  $(m_d + jm_q)$  for desired real and reactive power being injected to grid. The PI controller of d-loop and q-loop decides the dynamic response of the complete system. The reference for the d-loop  $(i_{dref})$  can be varied as per the real power being injected to grid, in general  $(i_{dref})$  derived from maximum power point algorithm. In this work,  $i_{qref}$  made equal to zero indicates the reactive power deliver to the grid is zero. With this the resultant inverter voltage  $(v_{inv})$  can be represented as:

$$v_{inv} = (V_{dg} - i_{qref}.\omega.L_f + \widetilde{V}_{dPI}) + j(V_{qg} + i_{dref}\omega L_f + \widetilde{V}_{qPI})$$

Considering the discussed criteria, the  $v_{inv}$  simplifies to

$$v_{inv} = (V_{dg} + \widetilde{V}_{dPI}) + j(i_{dref}\omega L_f + (\widetilde{V}_{q_{PI}} \approx 0))$$

(2.1)

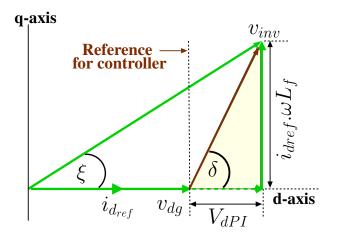

The phasors correspond to the position of the  $v_{inv}$  to deliver the designated active power to the grid is shown in Fig.2.2.

Figure 2.2: The phasor diagram representing the stiff grid scenario

### 2.2 The system dynamic assessment in weak grid scenario

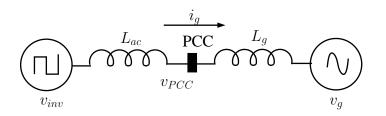

In the case of weak grid scenario, apart from the filter inductance  $L_f$  between the inverter and the PCC, the grid inductance  $L_g$  would present between PCC and the grid as shown in Fig.2.3. With the introduced  $L_g$  in weak grid scenario, the virtual inertial time constant

Figure 2.3: The simplified single line diagram to explain the weak grid scenario

of the filter loop can be viewed between the grid and the inverter as  $\frac{L_f+L_g}{R_g}$ . Here  $R_g$  is a virtual resistance correspond the power being injected to grid  $(V_{dg}/i_{dref})$ . With the deviated inertial time constant, the real (d-) and reactive (q-) axis deviated by  $\gamma$  angle and can be identified as new  $(d_w)$  and  $(q_w)$  axis as shown in Fig.2.4a. The axis transformation from d-axis to  $d_w$  axis can be represented with new inertial deviation angle correspond to grid injected current due to grid inductance  $(L_g)$  and grid resistance  $(R_g)$  as:

$$\gamma = \tan^{-1} \frac{i_{dref} . \omega . L_g}{i_{dref} . R_g} \qquad ; \gamma = \tan^{-1} \frac{\omega . L_g}{R_g}$$

(2.2)

In stiff grid scenario with reference to the d- and q-axis, the controller synthesize the  $\delta$  angle (Fig.2.2) to bring grid injected current in phase with the grid voltage  $V_{dg}$  at steady state. Whereas in the case of weak grid, the grid injected current can be derived with deviated inertial angle ( $\gamma$ ) as shown in Fig.2.4a with reference to stiff grid voltage ( $V_{inv}$ ) as:

$$i_{gw} = \frac{V_{inv}cos(\xi + \gamma)cos(\gamma) - V_{dg}}{R_g Cos(\gamma)}$$

(2.3)

From (2.3), it is evident that the when  $L_g$  equal to zero representing the stiff grid scenario, the  $i_{gw}=i_g=\frac{v_{inv}cos\xi-v_{PCC}}{R_g}$ . With the deviated current due to  $\gamma$ , the real voltage on the  $d_w$  axis can be identified as  $v_{inv_{dw}}=i_{gw}.R_g$  as shown in Fig.2.4a. Since the real and reactive power reference in d-q domain inline with  $V_{PCC}$ , the current  $(i_{gw})$  projections and corresponding power in the synchronous reference frame can be computed as:

$$\begin{bmatrix} i_{gd} \\ i_{gq} \end{bmatrix} = \begin{bmatrix} i_{gw} \end{bmatrix} \begin{bmatrix} \cos(\gamma) \\ \sin(\gamma) \end{bmatrix}; \begin{bmatrix} P_w \\ Q_w \end{bmatrix} = \begin{bmatrix} V_{PCC} i_{gw} \end{bmatrix} \begin{bmatrix} \cos(\gamma) \\ \sin(\gamma) \end{bmatrix}$$

(2.4)

With the deviated current  $(i_{gw})$  the PI controller can be expressed in a weak grid scenario as:

$$V_d^* = V_{d(PCC)} + (i_{dref} - i_{gw}.cos(\gamma))(K_p + K_i/s)$$

(2.5)

$$V_q^* = (-i_{gw}.sin(\gamma))(K_p + K_i/s)$$

(2.6)

$$V_{inv} = V_d^* + j V_q^* \tag{2.7}$$

Here the  $K_p$  indicates the proportional gain and  $K_i$  indicates the integral gain of the PI controller. With the deviated angle  $\gamma$  the controller would try to bring  $i_{gw}cos(\gamma)$  (referred onto d-axis) to  $i_{dref}$  as depicted in (2.5) in steady state to feed intended active power to the grid. Similarly in the q-axis, as depicted in (2.6), with the  $i_{qref} = 0$ , the current controller try to bring  $i_{gw}sin(\gamma)$  (referred onto q-axis) to zero as per the reactive power reference. As it is shown in (2.5) and (2.6), the the d and q-axis controllers are coupled

(c) With compensation in q-axis direction

Figure 2.4: The phasor diagram representing the inverter voltage, grid voltage and grid injected current in weak grid scenario

with the angle  $\gamma$ . At steady states, the d-and q-axis controllers would try to reach to corresponding real and reactive power reference. But due to coupling angle  $\gamma$ , the  $V_{inv}$ experience the oscillations. The nature of the oscillations are analyzed independently in d- and q-axis with help of phasors depicted in Fig.2.4b and Fig.2.4c respectively. In real power correction as shown in Fig.2.4b, the  $i_{gw}.R_g$  extended in the dw axis to match with the real power reference. In this process controller would deviate from  $v_{inv}$  (stiff grid with controller reference angle  $\delta$  shown in Fig.2.2) to  $v_{inv_{dw}}$  with angle of  $\delta_d$  as shown in Fig.2.4b. The deviated angle  $\delta_d$  can be computed as:

$$\psi_d = \tan^{-1} \frac{i_{gw} w. (L_g + L_f)}{i_{gw}.R_g} \quad ; \quad \gamma_d = \tan^{-1} \frac{i_{dref} w.L_g}{i_{dref}.R_g}$$

$$\delta_d = \tan^{-1} \frac{\omega.L_f.R_g}{R_g^2 - \omega^2 (L_g.L_f + L_g^2)} \tag{2.8}$$

At the same time the controller in q-loop  $(i_{gw}sin(\gamma))$  try to make equal to zero by aligning  $d_w$  axis to d-axis. In such case the position of  $V_{PCC}$  and  $v_{inv}$  variation with reference to stiff grid is shown in Fig.2.4c. In such scenario, the  $V_{inv}$  angle of deviation  $(\delta_q)$  from the stiff grid scenario in q-direction can be computed as:

$$\psi_q = \tan^{-1} \frac{i_{dref} w.(L_g + L_f)}{i_{dref}.R_g} \quad ; \quad \gamma_q = \tan^{-1} \frac{i_{dref} w.L_g}{i_{dref}.R_g}$$

$$\delta_q = \tan^{-1} \frac{\omega.L_f.R_g}{R_g^2 - \omega^2(L_g.L_f + L_g^2)} \tag{2.9}$$

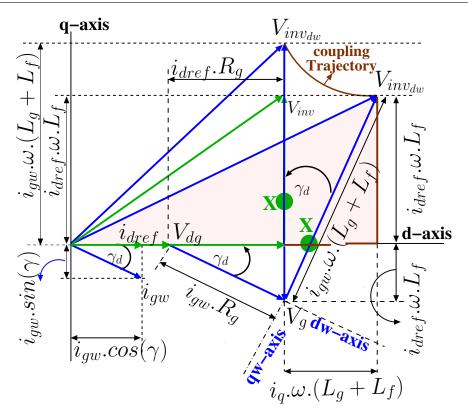

When both d-axis and q-axis controllers act together as per the real and reactive power references, the resultant oscillations derived through Fig.2.4b and Fig.2.4c is shown in Fig.2.5. The combined phasors shown in Fig.2.5 shows the voltage and grid injected current oscillations at the PCC. It represent the natural coupling between active and reactive power as depicted with the coupling trajectory shown in Fig.2.5 in a weak grid scenario with reference to coupling angle ( $\gamma$ ) as depicted in (2.4). From (2.8) and (2.9), it is evident that the oscillations at the PCC with reference to grid injected current  $i_g$ , the resultant system transfer function can be modeled as:

$$G(s) = \frac{R_g \cdot e^{-st}}{(L_g \cdot L_f + L_g^2)(s^2 + \frac{R_g \cdot L_f \cdot s}{L_g \cdot L_f + L_g^2} + \frac{R_g^2}{L_g \cdot L_f + L_g^2})}$$

(2.10)

The G(s) can be written in the form of  $\frac{\omega_n^2 e^{-st}}{R_g(s^2+2\delta\omega_n s+\omega_n^2)}$ , where  $\omega_n = \frac{R_g}{\sqrt{L_g.L_f+L_g^2}}$  and  $\delta = \frac{L_f}{2.\sqrt{L_g.L_f+L_g^2}}$ . With identified weak grid transfer function G(s), the complete closed loop signal flow diagram with the PI controller is shown in Fig.2.6.

Figure 2.5: The phasor diagram representing inverter voltage oscillations due to coupling between d-axis and q-axis compensation in weak grid scenario

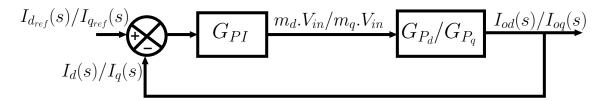

Figure 2.6: The simplified closed loop representation with the identified system transfer function and linear controller

### 2.3 The PI-controller modeling of plant for stable operation

The characteristic equation of the closed loop system can be derived from Fig.2.6 as:

$$\lambda(s) = 1 + (K_p + \frac{K_i}{s}) \cdot \frac{1}{R_q} \cdot \frac{\omega_n^2 \cdot e^{-st}}{s^2 + 2\delta\omega_n s + \omega_n^2}$$

(2.11)

$$\lambda(s) = R_g \cdot s(s^2 + 2\delta\omega_n s + \omega_n^2) + \omega_n^2 (K_p \cdot s + K_i)e^{-st}$$

$$(2.12)$$

$$\lambda^*(s) = e^{s\iota} \cdot \lambda(s) \quad and \ substituting \ s = j\omega$$

$$\lambda^*(j\omega) = j\omega R_g(-\omega^2 + j2\delta\omega_n\omega + \omega_n^2)e^{j\omega t} + \omega_n^2(K_p(j\omega) + K_i)$$

(2.13)

The characteristic equation can be decomposed into real and imaginary components as:

$$\lambda^*(j.\omega) = \lambda_r(\omega) + j\lambda_i(\omega) \tag{2.14}$$

$$\lambda_r(\omega) = R_g(\omega^3 - \omega\omega_n^2)\sin(\omega t) - 2\delta\omega_n\omega^2 R_g\cos(\omega t) + K_i.\omega_n^2$$

(2.15)

$$\lambda_i(\omega) = \omega (R_g(\omega_n^2 - \omega^2)\cos(\omega t) - 2\delta\omega_n \omega R_g \sin(\omega t) + K_p \omega_n^2)$$

(2.16)

Here 't' represents the sampling time interval of the controller. From (2.15) and (2.16) it is evident that the roots of the imaginary part  $(\lambda_i(\omega))$  of characteristic equation should goes to zero to make real roots. Therefore the tuning of  $K_p$  plays a vital role in controlling power oscillations at PCC. Through stability criteria mentioned in [63], the appropriate  $K_p$  value can be derived through the roots of the  $\lambda_i$ . To verify the system stability as per [63], the  $\lambda^*(s)$  is stable for any value of angle  $z_0$  ( $\omega t$ ) varying from  $[-\infty, +\infty]$  only when .

- 1. Condition-1 :  $E(z_0) = \lambda'_i(z_0) \cdot \lambda_r(z_0) \lambda_i(z_0) \lambda'_r(z_0) > 0$

- 2. Condition-2 :  $\lambda_r(z_0)$  and  $\lambda_i(z_0)$  have only simple real roots and are interlace

While finding the lower limit of  $K_p$  through condition-1 at obvious root  $z_0 = 0$ , the  $E(Z_0)$  can be written as:

$$E(0) = \lambda_r(0) \cdot \lambda'_i(0) = K_i \omega_n^2 (Rg\omega_n^2/t + K_p\omega_n^2/t) > 0$$

$$\implies K_p > -R_g \quad at \quad \omega_n > 0$$

(2.17)

The upper boundary of the  $K_p$  can be found through interlacing roots condition mentioned in condition-2 by making  $\lambda_i=0$ , that implies

$$R_g(\omega_n^2 - (z/t)^2)\cos(z) + K_p\omega_n^2 = 2\delta\omega_n\omega R_g\sin(z)$$

(2.18)

$$f(z) = g(z) \tag{2.19}$$