# The Write Problem: Challenges in Implementation of STT-RAM based LLCs

A Thesis Submitted

in Partial Fulfilment of the Requirements

for the Degree of

## DOCTOR OF PHILOSOPHY

by

## Prabuddha Sinha

(2019CSZ0008)

# DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY ROPAR

**APRIL**, 2025

Prabuddha Sinha: The Write Problem: Challenges in Implementation of STT-RAM based LLCs

Copyright ©2025, Indian Institute of Technology Ropar All Rights Reserved

Dedicated to my mother Dr. Niharika Sinha, my father Sanjib Sinha, and my sister Dr. Prayukta Sinha.

## **Declaration of Originality**

I hereby declare that the work that is being presented in the thesis entitled **The Write** Problem: Challenges in Implementation of STT-RAM based LLCs has been solely authored by me. It presents the result of my own independent investigation/research conducted during the time period from July 2019 to December 2024 under the supervision of Dr. Shirshendu Das, Assistant Professor, Indian Institute of Technology Hyderabad and Dr. Venkata Kalyan Tavva, Assistant Professor, Indian Institute of Technology Ropar. To the best of my knowledge, it is an original work, both in terms of research content and narrative, and has not been submitted or accepted elsewhere, in part or in full, for the award of any degree, diploma, fellowship, associateship, or similar title of any university or institution. Further, due credit has been attributed to the relevant state-of-the-art and collaborations (if any) with appropriate citations and acknowledgments, in line with established ethical norms and practices. I also declare that any idea/data/fact/source stated in my thesis has not been fabricated/falsified/misrepresented. All the principles of academic honesty and integrity have been followed. I fully understand that if the thesis is found to be unoriginal, fabricated, or plagiarized, the Institute reserves the right to withdraw the thesis from its archive and revoke the associated Degree conferred. Additionally, the Institute also reserves the right to appraise all concerned sections of society of the matter for their information and necessary action (if any). If accepted, I hereby consent for my thesis to be available online in the Institute's Open Access repository, inter-library loan, and the title & abstract to be made available to outside organizations.

Signature

Name: Prabuddha Sinha

Entry Number: 2019CSZ0008

Pralondalha Linha

Program: PhD

Department: Computer Science and Engineering

Indian Institute of Technology Ropar

Rupnagar, Punjab 140001

Date: April 17, 2025

## Acknowledgement

First and foremost, I would like to express my deepest sense of gratitude to my doctoral advisors, Dr. Shirshendu Das, and Dr. Venkata Kalyan Tavva for their invaluable guidance, unwavering support, and constant encouragement throughout the development of this thesis. Their expertise, insights, and thoughtful feedback have been instrumental in shaping my work. I am very lucky to have them as my guides on this beautiful journey. Dr. Shirshendu's limitless patience and fatherly advice during tough times has been a beacon of hope during this journey.

I also thank my collaborators/interns Krishna Pratik BV and Mangena Likhit Sai for their constant strive for excellence. I would also like to extend my sincere thanks to the members of my doctoral committee, Dr. Neeraj Goel and Dr. Nitin Auluck, Dr. Sudeepta Mishra, and Dr. Mahendra Sakare, for their insightful comments, suggestions, and for taking the time to review my work. Your input has greatly enriched the quality of this thesis.

I am deeply thankful to my family specially my late father, mother and sister for their unconditional love and support during this challenging journey. Your patience, understanding, and encouragement have provided me with the strength to persevere.

Special thanks to my lab members and colleagues of the CA-SIG Lab at CSE Department, IIT Ropar. I would particularly thank Prathamesh Nitin Tanksale, Waqar Hassan Mir, Jaspinder Kaur, Satya Jaswant Badri, Saurabh Jaiswal, Atul Kumar, Lalit Sharma and Pravesh Jamgade for the countless discussions, moral support, and the laughter that helped me navigate through stressful times. I am also thankful to my closest friends, Napendra Solanki and Gagan Sahoo who have been a constant through all my ups and downs during this course. The time spent together helped me recharge and continue to strive for excellence.

I express my gratitude to Prof. Rajeev Ahuja, the Honourable Director, Indian Institute of Technology Ropar, and the administration for providing all necessary administrative support and technical facilities required for carrying out the present research work. I also express my deep gratitude to the Head and entire faculty and staff members of the Department of Computer Science and Engineering, Indian Institute of Technology Ropar, for their continuous support and encouragement. Lastly, I would like to acknowledge the financial support provided by Qualcomm Incorporated through Qualcomm Faculty Award 2022 to my supervisor, Dr. Venkata Kalyan Tavva, without which this thesis would not have been possible.

This thesis is a culmination of not just my efforts, but also the collective efforts of everyone who has been part of my academic journey. I am deeply grateful for all your contributions. Thank you.

## Certificate

This is to certify that the thesis entitled **The Write Problem: Challenges in Implementation of STT-RAM based LLCs**, submitted by **Prabuddha Sinha (2019CSZ0008)** for the award of the degree of **Doctor of Philosophy** of Indian Institute of Technology Ropar, is a record of bonafide research work carried out under my guidance and supervision. To the best of my knowledge and belief, the work presented in this thesis is original and has not been submitted, either in part or fully, for the award of any other degree, diploma, fellowship, associate, or similar title from any university or institution.

In my opinion, the thesis has reached the standard of meeting the requirements of the regulations related to the degree.

Signature of the Supervisors:

Dr. Shirshendu Das Department of CSE

Indian Institute of Technology Hyderabad

Hyderabad, Telengana, 502284

Dr. Venkata Kalyan Tavva

Department of CSE

Indian Institute of Technology Ropar

Rupnagar, Punjab, 140001

Date: April 17, 2025

## Lay Summary

Non-volatile memory (NVM) based Last Level Caches (LLCs) are a viable alternative to the traditional Static Random Access Memory (SRAM) based LLCs. Implementing NVM based LLCs come with its own set of problems that mainly arises due to the writes. This thesis as the name suggests addresses and highlights the major issues that occur due to writes which prevent the implementation of an Spin Transfer Torque Random Access Memory (STT-RAM) based LLCs.

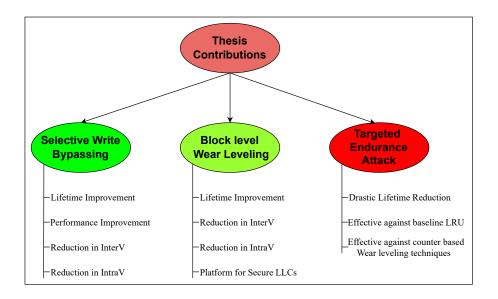

This thesis addresses the specific problems that arise due to the excessive uneven writes specifically lifetime degradation and performance degradation. The first work introduces two different techniques which aimed at wear leveling at the set level and way level granularity through write blocking and dynamic write bypassing. The second work proposes a decoupled cache architecture which is responsible for wear leveling at the block level granularity. The decoupled cache architecture also provides a platform for designing secured caches.

Another key part of the thesis is targeted endurance attacks that will be a security risk as any malicious attacker from a single core can target the shared LLC by focusing its writes to specific locations and drastically increasing the write count and thereby effecting the lifetime of the STT-RAM based LLC. The techniques are also effective against static and dynamic counter based wear leveling techniques.

## Abstract

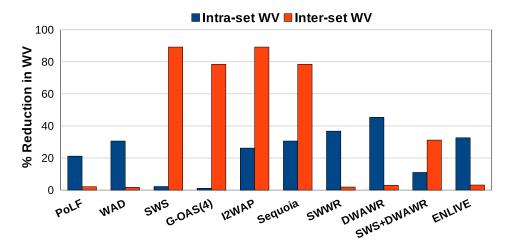

The design of Last Level Caches (LLCs) using Static Random Access Memory (SRAM) is increasingly being challenged by emerging memory technologies like Non-Volatile Memories (NVM). Among these, Spin-Transfer Torque RAM (STT-RAM) stands out for its higher density and lower static power consumption. However, its drawbacks—higher write latency, increased write power, and limited write endurance—pose significant challenges. The primary issue preventing widespread adoption of STT-RAM in LLCs is the low write endurance, largely caused by the uneven distribution of write operations across the cache. Existing techniques to address this focus on minimizing either inter-set (InterV) or intra-set (IntraV) write variation to prolong the lifetime of STT-RAM-based LLCs. Additionally, STT-RAM's high write latency can lead to congestion in the read-write queue of the LLC.

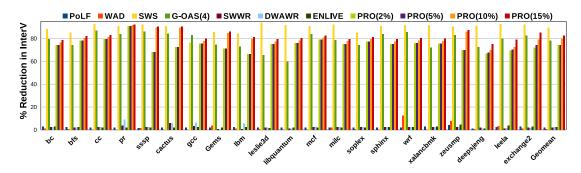

To address these challenges, two techniques have been proposed to enhance endurance while maintaining performance. The first, PROLONG, is a dynamic write bypassing approach that redirects write-backs from the L2 cache to an SRAM buffer or main memory. This decision is guided by two parameters: the write hotness of the cache set and the liveness score of the incoming block. The second, LiveWay, dynamically bypasses writes based on their placement in write-hot ways and their liveness scores. Both methods significantly improve wear leveling, reducing InterV and IntraV by approximately 84% and 53%, respectively, while achieving a Relative Lifetime Improvement (RLI) of up to 22×. Additionally, by alleviating write congestion in the read-write queue, these techniques minimize system impact, ensuring smoother performance.

Generic wear-leveling techniques primarily focus on extending LLC lifetime by reducing InterV and IntraV write variation, but block-level wear leveling remains rare. To address this gap, a decoupled cache architecture has been proposed. In this design, the Set-Associative SRAM tag array is separated from the Fully-Associative Data array, with the two linked via forward and backward pointers that maintain a 1:1 mapping. Two techniques are introduced within this architecture. The Primal Approach swaps writes between write-hot and write-cold blocks based on their write counts, with each block maintaining an individual write counter. The Hardware-Efficient Approach categorizes blocks into buckets using simple hashing. Writes from write-hot buckets are then redirected to write-cold buckets. These methods can achieve a RLI of up to  $13.07 \times$ .

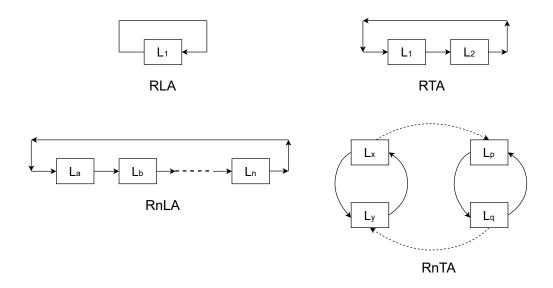

Malicious attacks in a multi-core setup require access to just one core to repeatedly target specific memory locations, leading to accelerated lifetime degradation. To expose this vulnerability in STT-RAM-based LLCs, we propose four distinct attacks: Recurring Location Attack (RLA), Recurring Toggle Attack (RTA), Random Location Attack (RnLA), and Random Toggle Attack (RnTA). These Targeted Endurance Attacks illustrate the impact of malicious benchmarks on modern counter-based wear-leveling techniques and reveal how wear leveling influences the effectiveness of such attacks.

**Keywords**: STT-RAM; Last Level Cache (LLC); InterV; IntraV; Wear leveling; Lifetime Improvement; Cache decoupling; Targeted Endurance Attack.

## List of Publications

#### **Journals**

- Prabuddha Sinha, Krishna Pratik BV, Shirshendu Das and Venkata Kalyan Tavva, "SmartDeCoup: Decoupling the STT-RAM LLC for even Write Distribution and Lifetime Improvement", in Elsevier Journal of System Architecture, February 2025. [DOI: https://doi.org/10.1016/j.sysarc.2025.103367]

- Sinha, 2. Prabuddha Mangena Likhit Sai, Shirshendu Das and Venkata Kalyan, "TENDRA: Targeted Attack Tavva Endurance in STT-RAM based LLCs", in IEEE Embedded Systems Letters. [DOI: https://doi.org/10.1109/LES.2024.3502297]

- 3. Sudershan Kumar, **Prabuddha Sinha**, and Shirshendu Das, "WinDRAM: Weak rows as in-DRAM cache", Concurrency and Computation: Practice and Experience 34, p.e.7350, 2022. [DOI: https://doi.org/10.1002/cpe.7350]

#### Conference Proceedings

- Prabuddha Sinha, Krishna Pratik BV, Shirshendu Das and Venkata Kalyan Tavva, "PROLONG: Priority based Write Bypassing Technique for Longer Lifetime in STT-RAM based LLC", in 10th International Symposium on Memory Systems (MEMSYS), Washington DC, USA, 2024. [DOI: https://doi.org/10.1145/3695794.3695803]

- 2. Prabuddha Sinha, Krishna Pratik BV, Shirshendu Das and Venkata Kalyan Tavva, "Hide-N-Seek: Hiding Writes in Buffer for Lifetime Improvement in STT-RAM based LLC", at HiPC 2023 Student Research Symposium, in Proceedings of the 2023 IEEE 30th International Conference on High Performance Computing, Data and Analytics Workshop (HiPCW), Goa, India, 2023, pp-84. [DOI: https://doi.org/10.1109/HiPCW61695.2023.00021]

- 3. Prabuddha Sinha, Krishna Pratik BV, Shirshendu Das and Venkata Kalyan Tavva, "LiveWay: Dynamic Write Bypassing for Lifetime Enhancement in STT-RAM LLC", at HiPC 2024 Student Research Symposium, in Proceedings of the 2024 IEEE 31st International Conference on High Performance Computing, Data and Analytics Workshop (HiPCW), Bangalore, India, 2024. [DOI: https://doi.ieeecomputersociety.org/10.1109/HiPCW63042.2024.00035]

## **Book Chapter**

Sudarshan Kumar, Prabuddha Sinha and Sujata Pal, "Crowd-Sourced Centralized Thermal Imaging for Isolation and Quarantine" in Computational Modeling and Data Analysis in COVID-19 Research, 2021, C. R. Panigrahi, B. Pati, M. Rath, and R. Buyya, Eds. CRC Press, ch. 8, p. 20. [DOI: https://doi.org/10.1201/9781003137481]

## List of Abbreviations and Notations

#### Abbreviations

AES Advanced Encryption Standard

APM Adaptive Placement and Migration

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processing Unit

DASCA Dead Write Prediction Assisted STT-RAM Cache

Architecture

DWAWR Dynamic Way Aware Write Restriction

DWWR Dynamic Window Write Restriction

DWM Domain Wall Memory E+R Evict and Reload E+T Evict and Reload

ECDSA Elliptic Curve Digital Signature Algorithm

ETB Embedded Trace Buffer

EViSC Enhanced Virtual Split Cache

F+F Flush and Flush F+R Flush and Reload

FSDRP Fellow Set with Dynamic Reserve Part FSSRP Fellow Set with Static Reserve Part

FT Flush Threshold GB Giga Bytes

GOAS Grouped On-access inter-set Swapping

HALLS Highly Adaptable Last-Level STT-RAM Cache

HC Hybrid Cache

HCA Hybrid Cache Architecture

IBTC Inclusive Bypass Tag Cache

IPC Instructions executed Per Cycle

KB Kilo Bytes

L1 Level 1

L2 Level 2

L3 Level 3

LHCA Inter-cache Level Hybrid Cache Architecture

LLC Last Level Cache

LRU Least Recently Used

LRU-CB Least Recently Used Cold Block

LSC Liveness Score Counter

MB Mega Bytes

MDB Multiple Dirty Bits

MM Main Memory

MPKI Misses per Kilo Instructions MTJ Magnetic Tunnel Junction

NIPC Normalized Instructions per Cycle

NP Normal Part of Cache NVM Non-Volatile Memory

NUCA Non-Uniform Cache Architecture

OAP An obstruction-aware cache management policy for

STT-RAM last-level caches

OAS On-Access Inter-Set Swapping

OS Operating System

PID Process Identifier

PoLF Probabilistic Set Line Flush

PTHCM Prediction Table-Based Cache Line Replacement and

Management Policy

P-ViSC Protean Virtual Split Cache

P+P Prime and Probe

PRO PROLONG

RAM Random Access Memory

RA Recently Accessed

RCR Recency-Aware Replacement

RFR Refresh-Aware Replacement

RLA Recurring Location Attack

RnLA Random Location Attack

RnTA Random Toggle Attack

RTA Recurring Toggle Attack

RQ Read Queue

RSA Rivest-Shamir-Adleman SRepl Swap-on-Replacement

SBAC Statistic-Based Write Bypassing Technique

SGX Software Guard Extensions

SLAM A hybrid last-level cache architecture

SRAM Static Random Access Memory

SRW Swap-on-Write

STT-RAM Spin-Transfer Torque RAM

SW Swap-on-Write SWS Swap Shift

TANC Trace Buffer Assisted Non-Volatile Memory Cache

TSX Hardware Transactional Memory

ViSC Virtual Split Cache VM Virtual Machine WAD Writeback Aware Displacement

WALL-NVC Write Aware Last Level Non-Volatile Cache

WCAB Write Congestion Aware Bypass

WH Write Hot

WIPE Wearout Informed Pattern Elimination

WL Write Latency

WQ Write Queue

## Notations

$AE_{pro}$  Additional Energy consumed by PROLONG

BPTR Backward Pointer

$E_{buff}$  Energy consumed by SRAM buffer

$E_{write}$  Energy saved by reducing the number of writes

FPTR Forward Pointer

$H_n$  n<sup>th</sup> Write Hot Bucket

InterV Inter-set Write Variation

IntraV Intra-set Write Variation

LSC Liveness Score Counter

LSn LSC value is 'n'

M Total number of cache ways N Total number of cache sets

*RL* Relative Lifetime

RLI Relative Lifetime Improvement

WCBkt Write Cold Bucket WCTR Write Counter WHBkt Write Hot Bucket WSC Writes Set Counter

$W_{avg}$  Average Writes in a cache block

$w_{i,j}$  Writes to a specific block of i<sup>th</sup> set and j<sup>th</sup> block

$W_{max}$  Maximum Writes in a cache block

# Contents

| D            | eclar  | ation                   |                                                 |   | iv               |

|--------------|--------|-------------------------|-------------------------------------------------|---|------------------|

| A            | cknov  | wledge                  | ement                                           |   | v                |

| $\mathbf{C}$ | ertifi | cate                    |                                                 |   | vi               |

| La           | ay Su  | ımmar                   | УУ                                              |   | vii              |

| $\mathbf{A}$ | bstra  | $\mathbf{ct}$           |                                                 |   | viii             |

| Li           | st of  | Publi                   | cations                                         |   | ix               |

| Li           | st of  | Abbr                    | eviations and Notations                         |   | x                |

| Li           | ist of | Figur                   | es                                              | 3 | cvii             |

| Li           | st of  | Table                   | ${f s}$                                         | X | xiii             |

| 1            | Intr   | oduct                   | ion                                             |   | 1                |

|              | 1.1    | 1.1.1<br>1.1.2<br>1.1.3 | STT-RAM LLCs                                    |   | 1<br>2<br>3<br>3 |

|              |        | 1.1.4                   | Wear Leveling Techniques                        |   | 4                |

|              | 1.2    | Motiv                   |                                                 |   | 4                |

|              | 1.3    | Summ                    | nary and Organization of the Thesis             |   | 5                |

| 2            | Bac    | kgrou                   | nd and Literature Review                        |   | 7                |

|              | 2.1    | Backg                   | ground                                          |   | 7                |

|              |        | 2.1.1                   | Cache Memories                                  |   | 7                |

|              |        | 2.1.2                   | STT-RAM Cell                                    |   | 8                |

|              |        | 2.1.3                   | STT-RAM based LLC                               |   | 9                |

|              | 2.2    | Write                   | Variation and Lifetime                          | • | 10               |

|              | 2.3    |                         | iques to Improve Lifetime in STT-RAM based LLCs |   | 11               |

|              |        | 2.3.1                   | Wear Leveling Techniques                        |   | 12               |

|              |        | 2.3.2                   | Write Bypassing Techniques                      |   | 15               |

|              |        | 2.3.3                   | Hybrid Caches                                   |   | 16               |

|              |        | 2.3.4                   | Miscellaneous Techniques                        |   | 18               |

|              |        | 2.3.5                   | Summary of this Section                         |   | 20               |

|              | 2.4    | Attacl                  | ks on STT-RAM LLCs                              |   | 21               |

**xiv** Contents

|                                                          |     | 2.4.1         | Cache Timing Channel Attacks                                      |

|----------------------------------------------------------|-----|---------------|-------------------------------------------------------------------|

|                                                          |     |               | 2.4.1.1 Cache Side Channel Attacks (SCA) 21                       |

|                                                          |     |               | 2.4.1.2 Cache Covert Channel Attacks (CCA)                        |

|                                                          |     | 2.4.2         | Cache Contention Attacks                                          |

|                                                          |     | 2.4.3         | Cache Occupancy Attacks                                           |

|                                                          |     | 2.4.4         | Cache Rowhammer based Attacks                                     |

|                                                          |     | 2.4.5         | Cache Miscellaneous Attacks                                       |

|                                                          |     | 2.4.6         | Summary of this Section                                           |

|                                                          | 2.5 | Summ          | ary of this Chapter                                               |

| 3 Dynamic Write Bypassing for Lifetime Improvement in ST |     |               | Write Bypassing for Lifetime Improvement in STT-RAM               |

|                                                          | LLC | $C\mathbf{s}$ | 25                                                                |

|                                                          | 3.1 | Introd        | uction                                                            |

|                                                          | 3.2 | Motiva        | ation                                                             |

|                                                          | 3.3 | PartA         | (To reduce InterV): PROLONG: Priority based Write Bypassing       |

|                                                          |     | Techn         | ique for Longer Lifetime in STT-RAM based LLC                     |

|                                                          |     | 3.3.1         | Proposed Architecture                                             |

|                                                          |     |               | 3.3.1.1 Writes set counter (WSC)                                  |

|                                                          |     |               | 3.3.1.2 SRAM Buffer                                               |

|                                                          |     |               | 3.3.1.3 Liveness Score Counter (LSC)                              |

|                                                          |     | 3.3.2         | Working of PROLONG                                                |

|                                                          |     | 3.3.3         | PROLONG Algorithm                                                 |

|                                                          | 3.4 | PartB         | (To reduce IntraV): LiveWay: Dynamic Write Bypassing for Lifetime |

|                                                          |     | Enhan         | acement in STT-RAM LLC                                            |

|                                                          |     | 3.4.1         | Proposed Architecture                                             |

|                                                          |     | 3.4.2         | Working of LiveWay                                                |

|                                                          | 3.5 | Exper         | imental Setup                                                     |

|                                                          |     | 3.5.1         | Simulator Setup                                                   |

|                                                          |     | 3.5.2         | Workloads                                                         |

|                                                          | 3.6 | PartA         | : Results and Analysis                                            |

|                                                          |     | 3.6.1         | Single-core Analysis                                              |

|                                                          |     | 3.6.2         | Multi-core Analysis                                               |

|                                                          |     | 3.6.3         | Sensitivity Analysis                                              |

|                                                          |     |               | 3.6.3.1 Importance of SRAM buffer                                 |

|                                                          |     |               | 3.6.3.2 Comparison with other write bypassing techniques 44       |

|                                                          |     |               | 3.6.3.3 Lifetime Comparison Analysis                              |

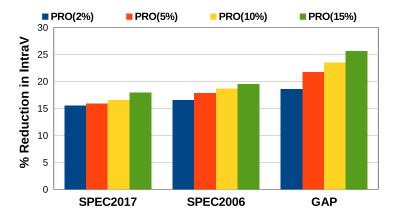

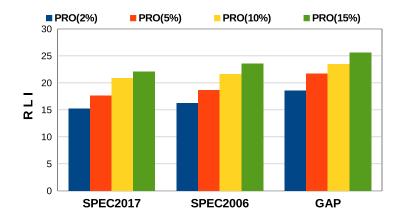

|                                                          |     |               | 3.6.3.4 SPEC2017 vs SPEC2006 vs GAP                               |

|                                                          |     | 3.6.4         | Hardware Overhead and Energy Consumption                          |

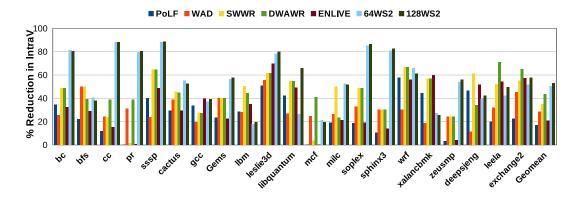

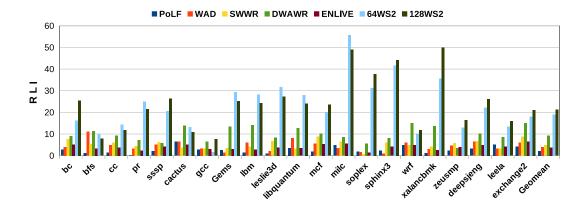

|                                                          | 3.7 | 0.0           | : Results and Analysis                                            |

|                                                          | -   | 3.7.1         | Single-core Analysis                                              |

|                                                          |     | 3.7.2         | Multi-core Analysis                                               |

|                                                          |     | 3.7.3         | SPEC2017 vs SPEC2006 vs GAP                                       |

|                                                          |     |               |                                                                   |

${f Contents}$

|   |     | 3.7.4  | Hardware Overhead and Energy Consumption                     | 52        |

|---|-----|--------|--------------------------------------------------------------|-----------|

|   | 3.8 | Conclu | usion                                                        | 54        |

| 4 | Dec | ouplin | ng the tag and data array for Lifetime Improvement           | <b>55</b> |

| _ | 4.1 |        | luction                                                      | 55        |

|   | 4.2 |        | ation                                                        | 55        |

|   | 4.3 |        | DeCoup                                                       | 57        |

|   | 2.0 | 4.3.1  | LLC Organization                                             | 57        |

|   |     | 1.0.1  | 4.3.1.1 Maintaining Coherence:                               | 58        |

|   |     | 4.3.2  | Primal Approach                                              |           |

|   |     |        | 4.3.2.1 Working Example                                      |           |

|   |     |        | 4.3.2.2 Drawbacks of Primal Approach                         | 61        |

|   |     | 4.3.3  | Hardware Efficient Approach                                  | 61        |

|   |     |        | 4.3.3.1 Bucket formation                                     | 62        |

|   |     |        | 4.3.3.2 Working Example                                      |           |

|   |     | 4.3.4  | Primal Approach vs Hardware Efficient Approach               | 64        |

|   |     | 4.3.5  | Importance of SmartDeCoup in Modern LLC                      | 64        |

|   |     |        | 4.3.5.1 Challenges in Implementing SmartDeCoup on Mirage and |           |

|   |     |        | Maya-Cache:                                                  | 65        |

|   |     |        | 4.3.5.2 SmartDeCoup with non-decoupled secured LLC designs   | 65        |

|   | 4.4 | Exper  | iments                                                       | 66        |

|   |     | 4.4.1  | Simulator Setup                                              | 66        |

|   |     | 4.4.2  | Workloads                                                    | 68        |

|   | 4.5 | Result | ts and Analysis                                              | 68        |

|   |     | 4.5.1  | Primal Approach                                              | 69        |

|   |     |        | 4.5.1.1 Single-core Analysis                                 | 70        |

|   |     |        | 4.5.1.2 Multi-core Analysis                                  | 72        |

|   |     | 4.5.2  | Hardware Efficient Approach                                  | 74        |

|   |     |        | 4.5.2.1 Single-core Analysis                                 | 74        |

|   |     |        | 4.5.2.2 Multi-core Analysis                                  | 76        |

|   |     | 4.5.3  | Sensitivity Analysis                                         | 78        |

|   |     |        | 4.5.3.1 Primal Approach vs Hardware Efficient Approach       | 78        |

|   |     |        | 4.5.3.2 SPEC2017 vs SPEC2006 vs GAP                          | 80        |

|   |     |        | 4.5.3.3 Analysis of AI Workloads                             | 82        |

|   |     | 4.5.4  | Overhead Analysis                                            | 83        |

|   | 4.6 | Concl  | usion                                                        | 85        |

| 5 | End | luranc | e Attacks on STTRAM LLCs                                     | 87        |

|   | 5.1 |        | luction                                                      | 87        |

|   | 5.2 |        | ation                                                        | 88        |

|   | 5.3 |        | ORA: Targeted Endurance Attack                               | 89        |

|   |     | 5.3.1  | Threat Model                                                 | 89        |

xvi

|                           |       | 5.3.2  | The Att   | ack Idea                                            |      |   | 90  |

|---------------------------|-------|--------|-----------|-----------------------------------------------------|------|---|-----|

|                           |       |        | 5.3.2.1   | Recurring Location Attack (RLA)                     |      |   | 90  |

|                           |       |        | 5.3.2.2   | Recurring Toggle Attack (RTA)                       |      |   | 91  |

|                           |       |        | 5.3.2.3   | Random Location Attack (RnLA)                       |      |   | 92  |

|                           |       |        | 5.3.2.4   | Random Toggle Attack (RnTA)                         |      |   | 93  |

|                           |       | 5.3.3  | Compari   | ison between Attacks                                |      |   | 94  |

|                           | 5.4   | Experi | imental E | valuation                                           |      |   | 96  |

|                           |       | 5.4.1  | Simulate  | or Setup                                            |      |   | 96  |

|                           |       | 5.4.2  | Workloa   | $\mathrm{ds}$                                       |      |   | 96  |

|                           | 5.5   | Result | s and An  | alysis                                              |      |   | 97  |

|                           |       | 5.5.1  | Effects o | f RLA, RTA, RnLA and RnTA on different State-of-th  | e-ar | t |     |

|                           |       |        | Wear Le   | veling Techniques                                   |      |   | 97  |

|                           |       |        | 5.5.1.1   | Write Count                                         |      |   | 107 |

|                           |       | 5.5.2  | Effects o | on Lifetime and Performance                         |      |   | 108 |

|                           | 5.6   | Conclu | sion and  | Future Work                                         |      |   | 109 |

| 6                         | Con   | clusio | n and Fu  | ature Scope                                         |      |   | 111 |

|                           | 6.1   | Major  | Research  | Contributions                                       |      |   | 111 |

|                           | 6.2   | Future | Scope .   |                                                     |      |   | 112 |

|                           |       | 6.2.1  | Practica  | l Lifetime Improvement for Industry-wide Adaptation |      |   | 113 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces   |           |                                                     |      |   | 115 |

# List of Figures

| 1.1  | Memory Organization and Hierarchy                                          | 1  |

|------|----------------------------------------------------------------------------|----|

| 2.1  | A generic Set-Associative LLC                                              | 8  |

| 2.2  | Layout of an STT-RAM cell                                                  | 9  |

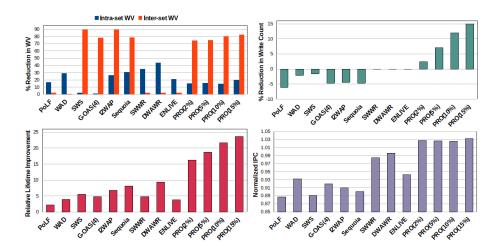

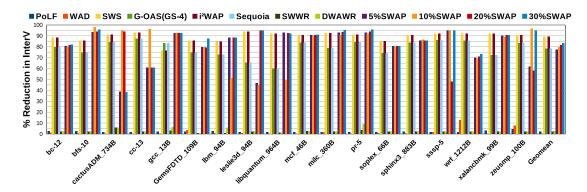

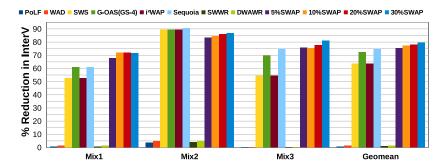

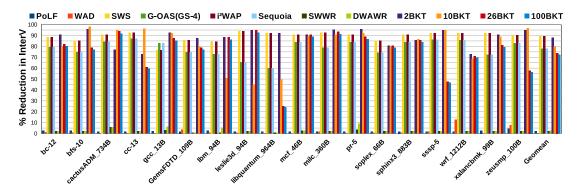

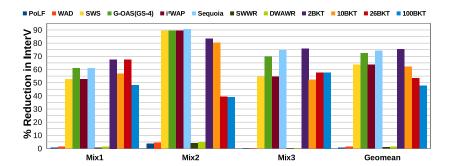

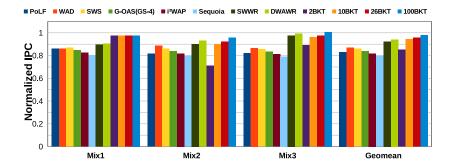

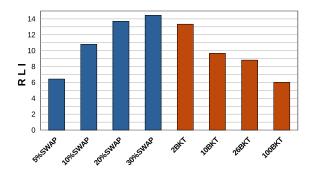

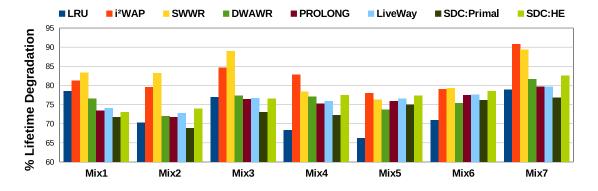

| 3.1  | Reduction in InterV and IntraV for various state-of-the-art wear leveling  |    |

|      | techniques                                                                 | 26 |

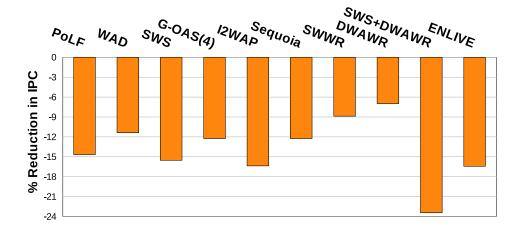

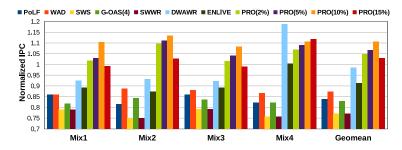

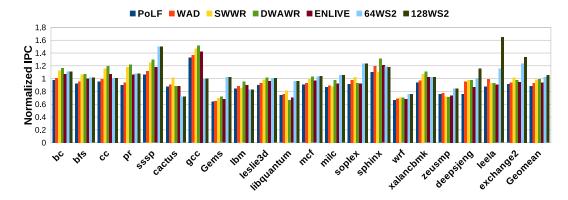

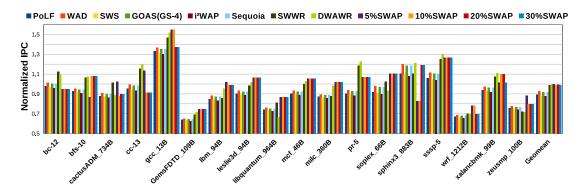

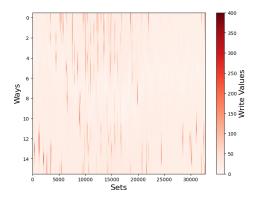

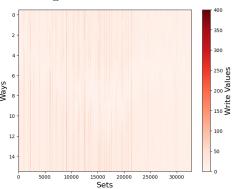

| 3.2  | IPC Degradation for various state-of-the-art wear leveling techniques      | 26 |

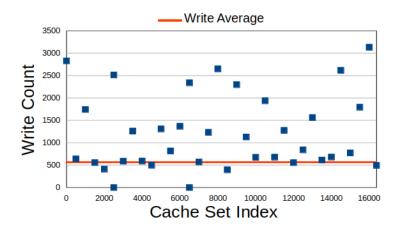

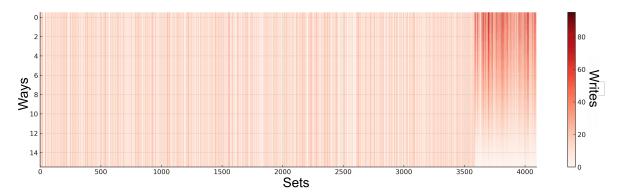

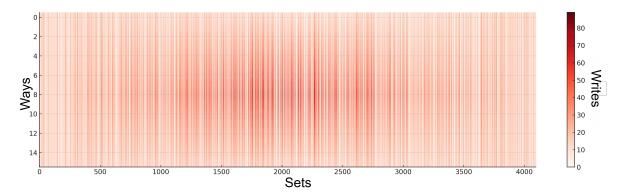

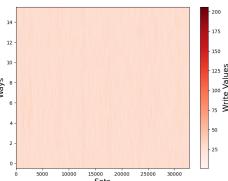

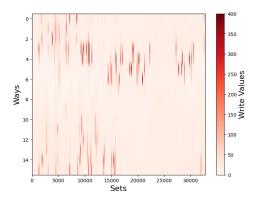

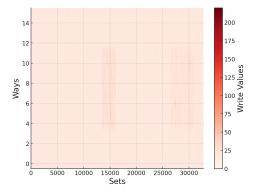

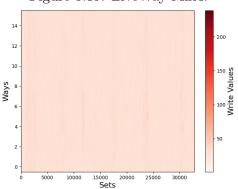

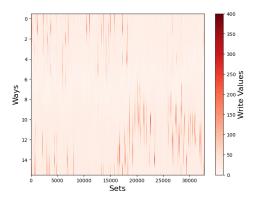

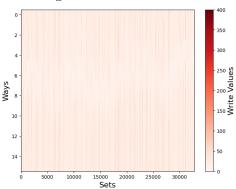

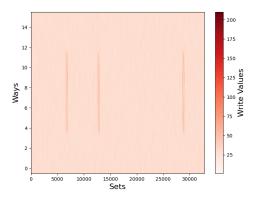

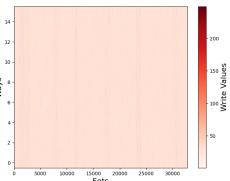

| 3.3  | Non-uniform write distribution across cache sets                           | 28 |

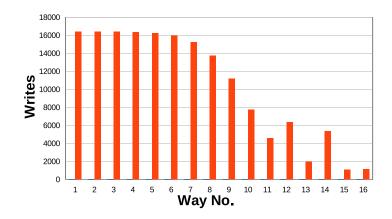

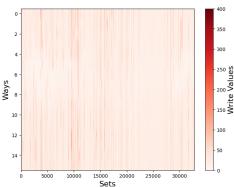

| 3.4  | Non-uniform write distribution across cache ways                           | 28 |

| 3.5  | Average Write Distribution in STT-RAM based LLC with LRU among the         |    |

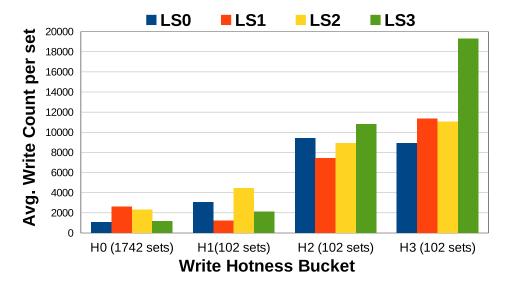

|      | Write Hot (WH) buckets (15%) with Liveness Score (LS)                      | 32 |

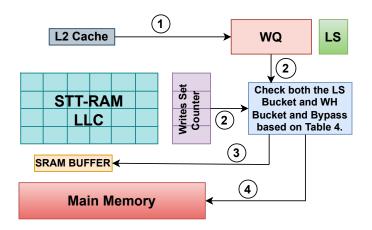

| 3.6  | Architecture and Steps in PROLONG Algorithm                                | 33 |

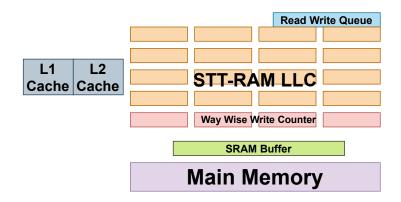

| 3.7  | Proposed Architecture of LiveWay                                           | 34 |

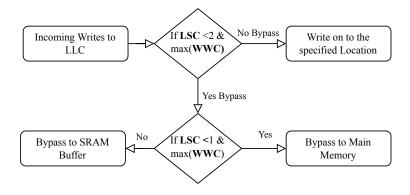

| 3.8  | Flowchart of the Proposed Algorithm for LiveWay                            | 34 |

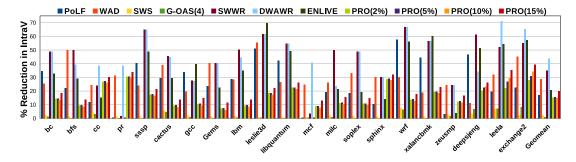

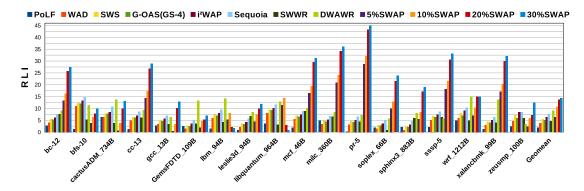

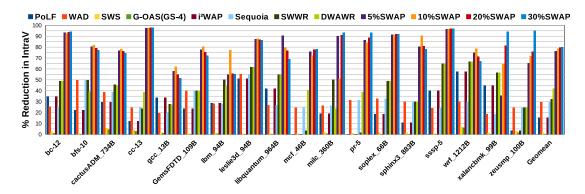

| 3.9  | Percentage Reduction in InterV in Single-core System (higher the better)   | 37 |

| 3.10 | Percentage Reduction in IntraV in Single-core System (higher the better)   | 38 |

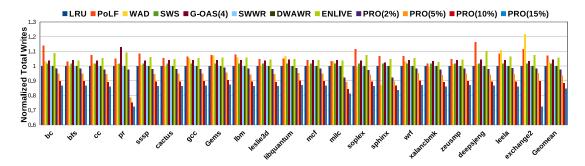

| 3.11 | Comparison of Normalized Total Write Count in single-core Systems (lower   |    |

|      | is better)                                                                 | 39 |

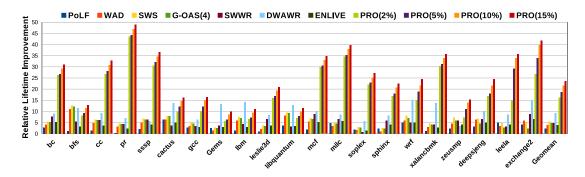

| 3.12 | Comparison of Relative Lifetime Improvement in single-core Systems         |    |

|      | (higher the better)                                                        | 39 |

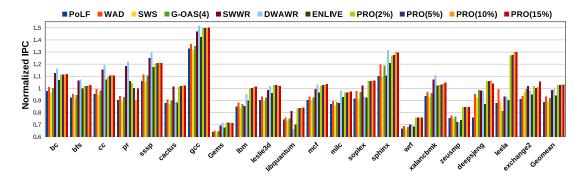

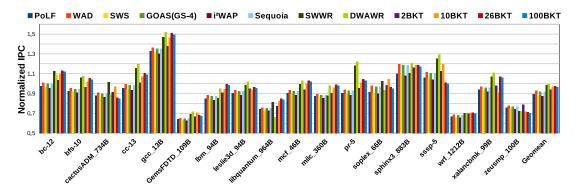

| 3.13 | Comparison of Normalized IPC in single-core Systems (higher the better)    | 40 |

| 3.14 | Average Comparison of PROLONG in Single-core Systems with                  |    |

|      | state-of-the-art                                                           | 40 |

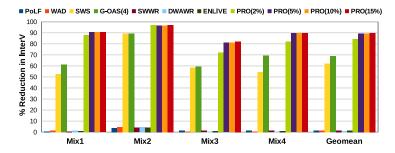

| 3.15 | Percentage Reduction in InterV for Multicore Systems (higher the better)   | 41 |

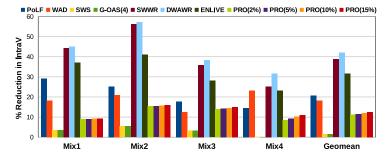

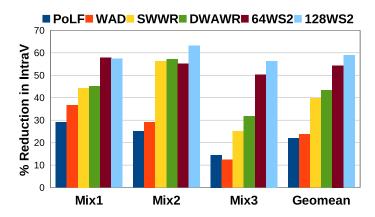

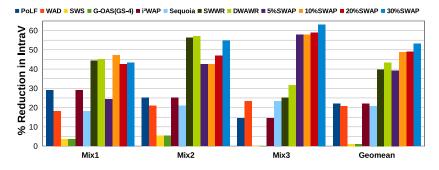

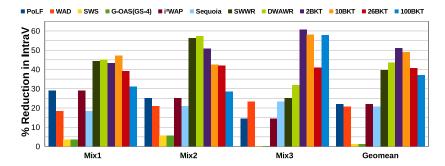

| 3.16 | Percentage Reduction in IntraV for Multi-core Systems (higher the better). | 41 |

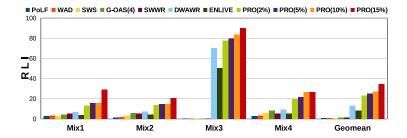

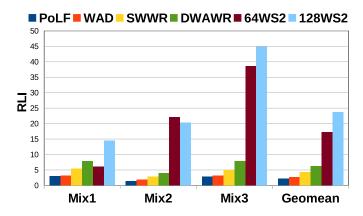

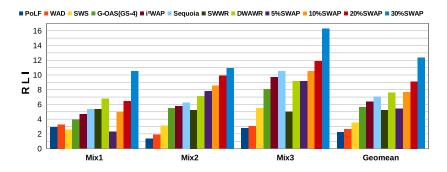

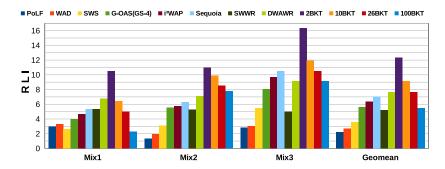

| 3.17 | Relative Lifetime Improvement (RLI) for Multi-core Systems (higher the     |    |

|      | better)                                                                    | 41 |

| 3.18 | Normalized Total Writes w.r.t. baseline (LRU) for Multi-core Systems       |    |

|      | (lower is better)                                                          | 42 |

| 3.19 | Normalized IPC w.r.t. baseline (LRU) for Multi-core Systems (higher the    |    |

|      | better)                                                                    | 42 |

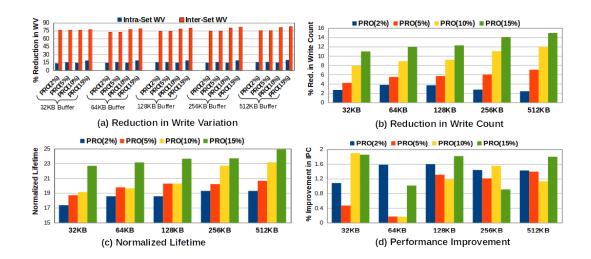

| 3.20 | Comparison of different PROLONG configurations with baseline in a          |    |

|      | single-core environment. $PRO(x\%)$ means the bypass aggressiveness of     |    |

|      | PROLONG is $x\%$ . Each bypass aggressiveness value is experimented with   |    |

|      | 32KB, 64KB, 128KB, 256KB, and 512KB of buffer size                         | 43 |

xviii List of Figures

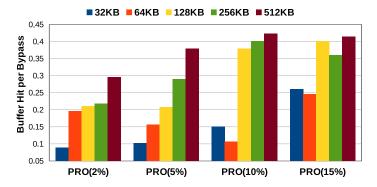

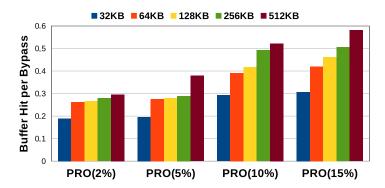

| 3.21 | the better)                                                                        | 44 |

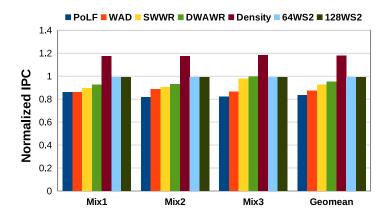

|------|------------------------------------------------------------------------------------|----|

| 3.22 | Buffer hit per write bypass in different configurations of PROLONG for AI          |    |

|      | workloads (higher the better)                                                      | 45 |

| 3.23 | Comparison of Normalized Lifetime of PROLONG with Density (higher the              |    |

|      | better)                                                                            | 45 |

| 3.24 | Comparison of Normalized IPC of PROLONG with Density (higher the                   |    |

|      | better)                                                                            | 45 |

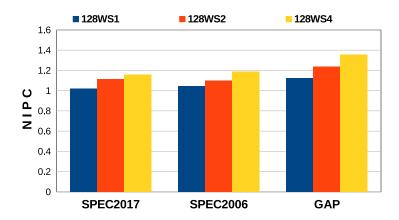

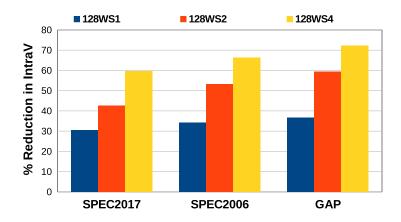

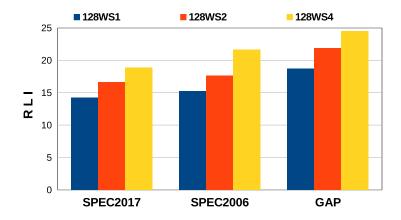

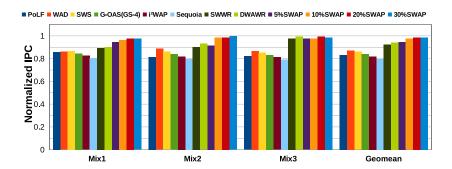

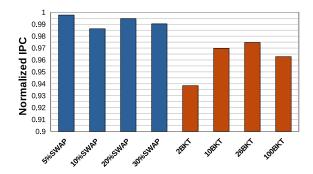

| 3.25 | Normalized IPC of various different benchmarks run on various configurations.      | 48 |

| 3.26 | Reduction in InterV of various different benchmarks run on various                 |    |

|      | configurations                                                                     | 48 |

| 3.27 | Reduction in IntraV of various different benchmarks run on various                 |    |

|      | configurations                                                                     | 48 |

| 3.28 | RLI of various different benchmarks run on various configurations                  | 49 |

| 3.29 | % Reduction in Intra<br>V for Single-core Systems (Higher the better)              | 49 |

| 3.30 | Relative Lifetime Improvement (RLI) (in times) for Single-core Systems             |    |

|      | (Higher the better)                                                                | 50 |

| 3.31 | Geomean Normalized IPC for Single-core Systems (Higher the better)                 | 50 |

| 3.32 | % Reduction in IntraV for Multi-core Systems                                       | 51 |

| 3.33 | Relative LI (in times) for Multi-core Systems                                      | 51 |

| 3.34 | Normalized IPC for Multi-core Systems                                              | 52 |

| 3.35 | Normalized IPC of various different benchmarks run on various configurations.      | 53 |

| 3.36 | Reduction in IntraV of various different benchmarks run on various                 |    |

|      | configurations                                                                     | 53 |

| 3.37 | RLI of various different benchmarks run on various configurations                  | 53 |

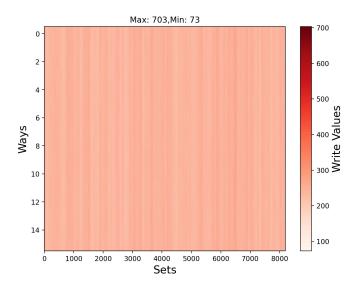

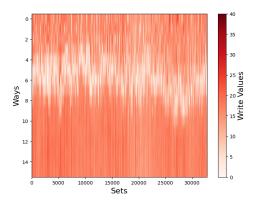

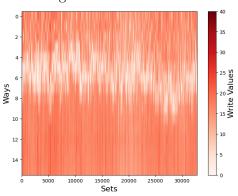

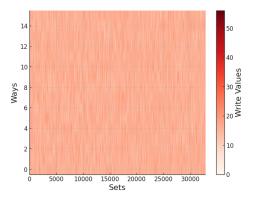

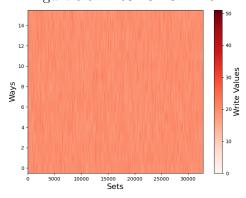

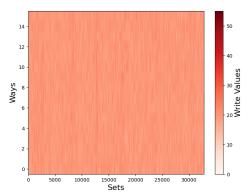

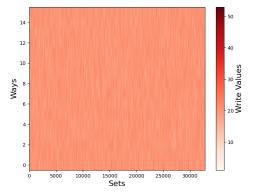

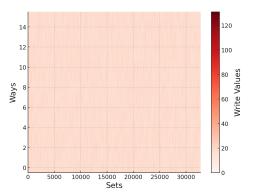

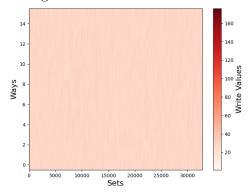

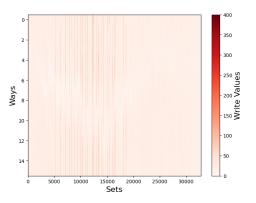

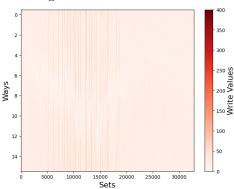

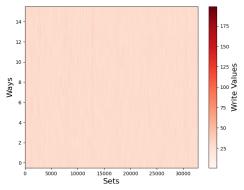

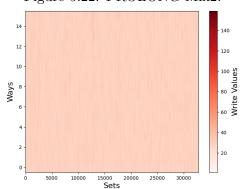

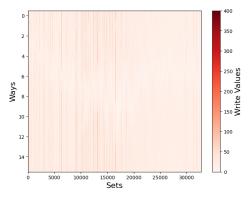

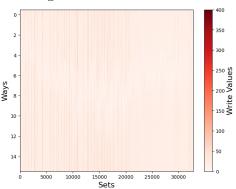

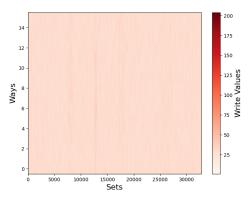

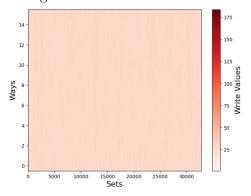

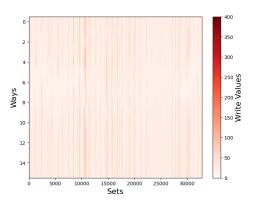

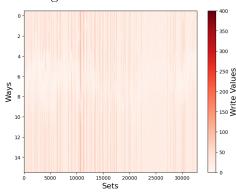

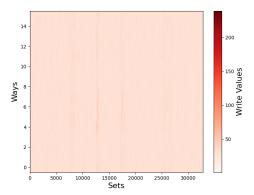

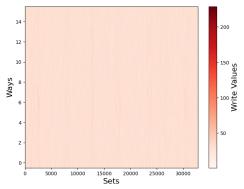

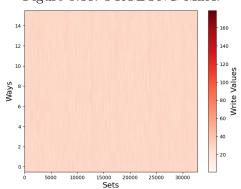

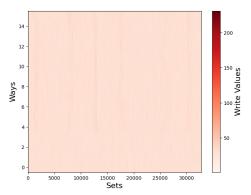

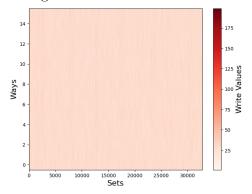

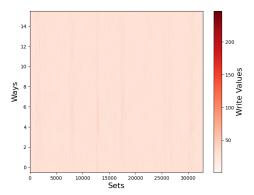

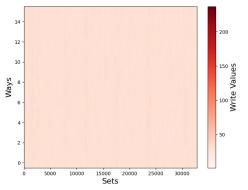

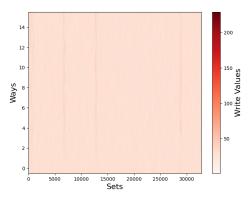

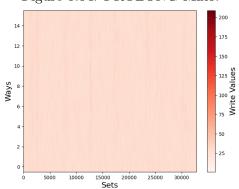

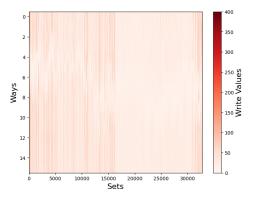

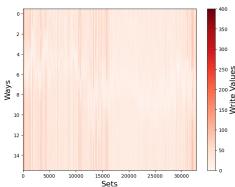

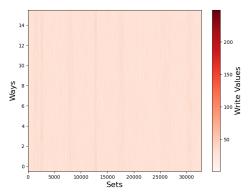

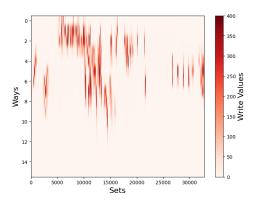

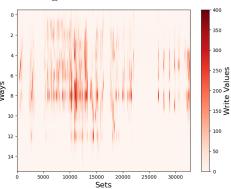

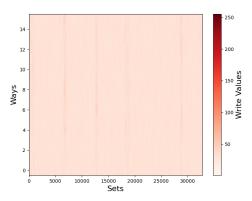

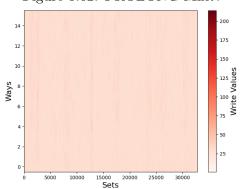

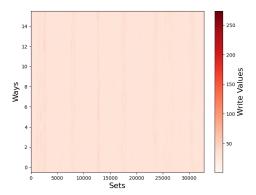

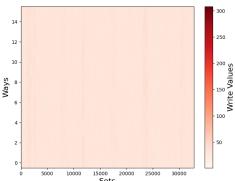

| 4.1  | Heatmap representing the non-uniform write distribution at LLC for a               |    |

|      | single-core $milc$ run                                                             | 56 |

| 4.2  | The proposed decoupled cache                                                       | 59 |

| 4.3  | Working Example of the Primal Approach                                             | 61 |

| 4.4  | Working Example of the Hardware Efficient Approach                                 | 63 |

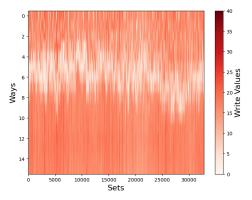

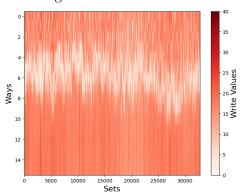

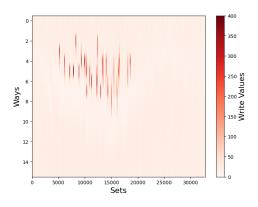

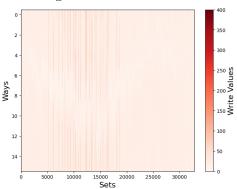

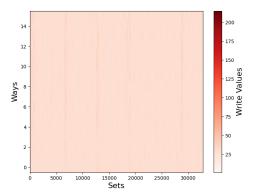

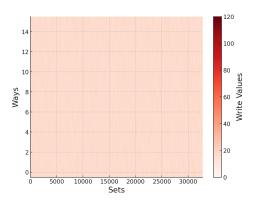

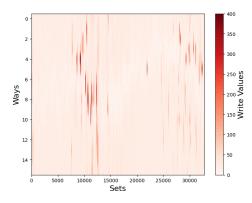

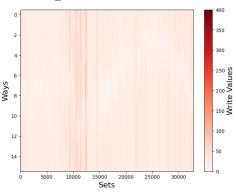

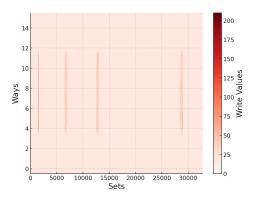

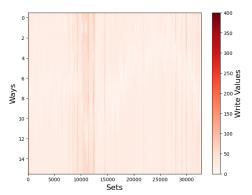

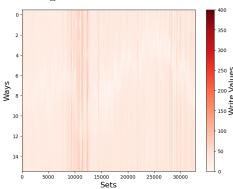

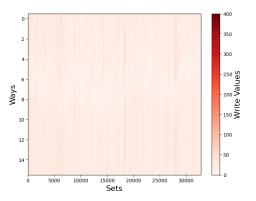

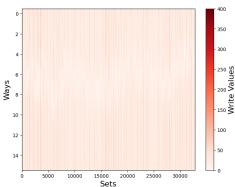

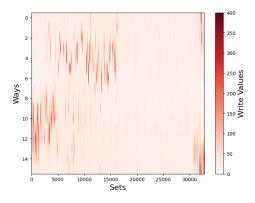

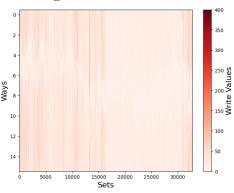

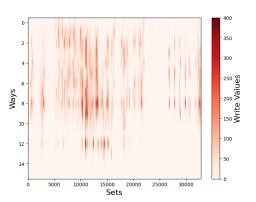

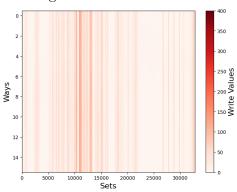

| 4.5  | Write Distribution for Epoch 1 for Primal Approach on SWAP 10%                     | 69 |

| 4.6  | Write Distribution for Epoch 2 for Primal Approach on SWAP 10%                     | 69 |

| 4.7  | Write Distribution for Epoch 3 for Primal Approach on SWAP 10%                     | 69 |

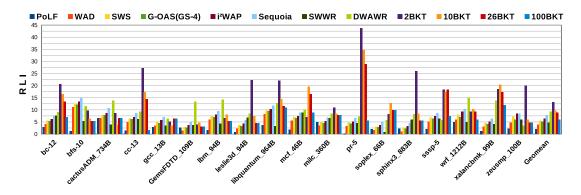

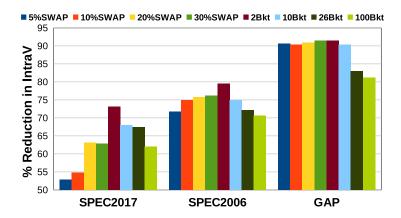

| 4.8  | Relative Lifetime Improvement in single-core systems for <i>Primal Approach</i> .  | 70 |

| 4.9  | Percentage reduction of IntraV in single-core systems for <i>Primal Approach</i> . | 71 |

| 4.10 | Percentage reduction of InterV in single-core systems for <i>Primal Approach</i> . | 71 |

| 4.11 | Normalized IPC in single-core systems for $Primal\ Approach.$                      | 71 |

| 4.12 | Relative Lifetime Improvement in multi-core systems for $Primal\ Approach$ .       | 72 |

| 4.13 | Percentage reduction of IntraV in multi-core systems for <i>Primal Approach</i> .  | 72 |

| 4.14 | Percentage reduction of InterV in multi-core systems for $Primal\ Approach$ .      | 73 |

| 4.15 | Normalized IPC in multi-core systems for <i>Primal Approach</i>                    | 73 |

List of Figures xix

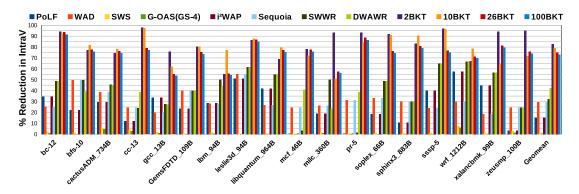

| 4.16  | Relative Lifetime Improvement in single-core systems for <i>Hardware Efficient Approach</i>  | 74       |

|-------|----------------------------------------------------------------------------------------------|----------|

| 4.17  | Percentage Reduction of IntraV in single-core systems for <i>Hardware Efficient Approach</i> | 75       |

| 4.18  | Percentage Reduction of InterV in single-core systems for <i>Hardware Efficient Approach</i> | 75       |

| 4.19  | Normalized IPC in single-core systems for Hardware Efficient Approach                        | 75       |

| 4.20  | Relative Lifetime Improvement in multi-core systems for <i>Hardware Efficient</i>            | 77       |

| 4 91  | Approach                                                                                     | 77       |

| 4.21  | Percentage Reduction of IntraV in multi-core systems for <i>Hardware Efficient Approach</i>  | 77       |

| 4 22  | Percentage Reduction of InterV in multi-core systems for Hardware Efficient                  | 11       |

| 4.22  | Approach                                                                                     | 77       |

| 4 23  | Normalized IPC in multi-core systems for Hardware Efficient Approach                         | 77       |

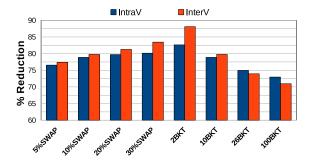

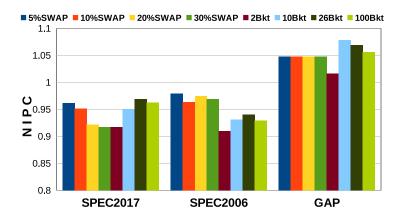

|       | Comparison of Reduction in IntraV and InterV in a Single-core System                         | 79       |

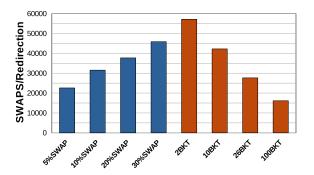

|       | Comparison of Redirection/SWAP Count in a Single-core System                                 | 79       |

|       | Comparison of Relative Lifetime Improvement in a Single-core System                          | 79       |

|       | Comparison of Normalized IPC in a Single-core System                                         | 79       |

|       | Normalized IPC of various different benchmarks run on various                                |          |

|       | configurations of our proposed approaches                                                    | 81       |

| 4.29  | Reduction in IntraV of various different benchmarks run on various                           |          |

|       | configurations of our proposed approaches                                                    | 82       |

| 4.30  | Reduction in InterV of various different benchmarks run on various                           |          |

|       | configurations of our proposed approaches                                                    | 82       |

| 4.31  | RLI of various different benchmarks run on various configurations of our                     |          |

|       | proposed approaches                                                                          | 82       |

| 4.32  | RLI of AI workloads on various configurations                                                | 83       |

| 4.33  | % Reduction of InterV and IntraV of AI workloads on various configurations.                  | 83       |

| 5.1   | Visualization of the Different Types of Targeted Endurance Attacks                           | 95       |

| 5.2   | LRU-Mix0                                                                                     | 98       |

| 5.3   | i <sup>2</sup> WAP-Mix0                                                                      | 98       |

| 5.4   | SWWR-Mix0                                                                                    | 98       |

| 5.5   | DWAWR-Mix0                                                                                   | 98       |

| 5.6   | PROLONG-Mix0.                                                                                | 98       |

| 5.7   | LiveWay-Mix0                                                                                 | 98       |

| 5.8   | SDC:Primal-Mix0.                                                                             | 98       |

| 5.9   | SDC:HE-Mix0                                                                                  | 98       |

|       | LRU-Mix1                                                                                     | 99       |

|       | i <sup>2</sup> WAP-Mix1                                                                      | 99       |

|       |                                                                                              | 99<br>99 |

| U. IU |                                                                                              | 00       |

xx List of Figures

| 5.14 | PROLONG-Mix1            |

|------|-------------------------|

| 5.15 | LiveWay-Mix1            |

| 5.16 | SDC:Primal-Mix1         |

| 5.17 | SDC:HE-Mix1             |

| 5.18 | LRU-Mix2                |

| 5.19 | $i^2WAP-Mix2.$          |

| 5.20 | SWWR-Mix2               |

| 5.21 | DWAWR-Mix2              |

| 5.22 | PROLONG-Mix2            |

| 5.23 | LiveWay-Mix2            |

| 5.24 | SDC:Primal-Mix2         |

| 5.25 | SDC:HE-Mix2             |

| 5.26 | LRU-Mix3                |

|      | $i^2WAP-Mix3.$          |

| 5.28 | SWWR-Mix3               |

| 5.29 | DWAWR-Mix3              |

| 5.30 | PROLONG-Mix3            |

| 5.31 | LiveWay-Mix3            |

| 5.32 | SDC:Primal-Mix3         |

| 5.33 | SDC:HE-Mix3             |

|      | LRU-Mix4                |

| 5.35 | $i^2WAP-Mix4.$          |

| 5.36 | SWWR-Mix4               |

|      | DWAWR-Mix4              |

| 5.38 | PROLONG-Mix4            |

| 5.39 | LiveWay-Mix4            |

| 5.40 | SDC:Primal-Mix4         |

| 5.41 | SDC:HE-Mix4             |

| 5.42 | LRU-Mix5                |

|      | $i^2WAP-Mix5.$          |

| 5.44 | SWWR-Mix5               |

| 5.45 | DWAWR-Mix5              |

| 5.46 | PROLONG-Mix5            |

| 5.47 | LiveWay-Mix5            |

| 5.48 | SDC:Primal-Mix5         |

| 5.49 | SDC:HE-Mix5             |

| 5.50 | LRU-Mix6                |

| 5.51 | i <sup>2</sup> WAP-Mix6 |

|      | SWWR-Mix6               |

| 5.53 | DWAWR-Mix6              |

| 5.54 | PROLONG-Mix6            |

| T : 1 C TI:      | •   |

|------------------|-----|

| List of Figures  | XXI |

| 2000 0, 2 0, 400 |     |

| 5.55 LiveWay-Mix6                |

|----------------------------------|

| 5.56 SDC:Primal-Mix6             |

| 5.57 SDC:HE-Mix6                 |

| 5.58 LRU-Mix7                    |

| 5.59 i <sup>2</sup> WAP-Mix7     |

| 5.60 SWWR-Mix7                   |

| 5.61 DWAWR-Mix7                  |

| 5.62 PROLONG-Mix7                |

| 5.63 LiveWay-Mix7                |

| 5.64 SDC:Primal-Mix7             |

| 5.65 SDC:HE-Mix7                 |

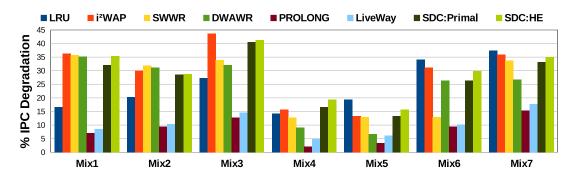

| 5.66 Degradation in Lifetime     |

| 5.67 Degradation in IPC          |

|                                  |

| 6.1 Graphical Overview of Thesis |

xxii List of Figures

# List of Tables

| 2.1<br>2.2 | Comparison of SRAM cell and STT-RAM cell (R/W=Read/Write) Classification and Brief Overview of Lifetime Enhancement Techniques | 10 |

|------------|--------------------------------------------------------------------------------------------------------------------------------|----|

|            | for NVM based LLC (LI=Lifetime Improvement, RedInterV=Reduction                                                                |    |

|            | in InterV, RedIntraV=Reduction in IntraV and PI=Performance                                                                    |    |

|            | Improvement and Energy Reduction=ER)                                                                                           | 20 |

| 2.3        | Classification of LLC Attacks                                                                                                  | 23 |

| 3.1        | Bucket Distribution among sets based on Liveness Score (LS)                                                                    | 30 |

| 3.2        | Bucket Distribution among sets based on Write Counter                                                                          | 31 |

| 3.3        | Write Bypassing based on Write Hot Sets (WH) and LSC Buckets                                                                   | 32 |

| 3.4        | Simulation parameters of the baseline single-core system                                                                       | 35 |

| 3.5        | Different PROLONG configurations used                                                                                          | 36 |

| 3.6        | Workloads for single-core system                                                                                               | 36 |

| 3.7        | Workloads for Quad-Core System                                                                                                 | 37 |

| 3.8        | The important hardware parameters of the SRAM buffer used in                                                                   |    |

|            | PROLONG. The parameters are extracted from CACTI [1]                                                                           | 43 |

| 3.9        | Normalized Lifetime of Write Intensive Workloads                                                                               | 46 |

| 3.10       | Storage Overhead of Prolong                                                                                                    | 49 |

| 3.11       | Storage Overhead of LiveWay                                                                                                    | 54 |

| 4.1        | Simulation parameters of the baseline single-core system                                                                       | 66 |

| 4.2        | Configurations of <i>Primal</i> and <i>Hardware Efficient Approaches.</i>                                                      | 67 |

| 4.3        | Thresholds for Switching in different bucket count for <i>Hardware Efficient</i>                                               |    |

|            | Approaches                                                                                                                     | 67 |

| 4.4        | Write Intensive Workloads for single-core system                                                                               | 68 |

| 4.5        | Workloads for Quad-Core System                                                                                                 | 68 |

| 4.6        | Geomean Comparisons for Single-core Systems with <i>Primal Approach</i>                                                        | 72 |

| 4.7        | Geomean Comparisons for Multi-core Systems with $Primal\ Approach.$                                                            | 74 |

| 4.8        | Geomean Comparisons for Single-core Systems with Hardware Efficient                                                            |    |

|            | Approach                                                                                                                       | 76 |

| 4.9        | Geomean Comparisons for Multi-core Systems with Hardware Efficient                                                             |    |

|            | Approach                                                                                                                       | 78 |

| 4.10       | Comparisons of various configurations of the proposed technique with                                                           |    |

|            | varying cache sizes                                                                                                            | 80 |

| 4.11       | Storage Overhead of Proposed Techniques                                                                                        | 84 |

| 5.1        | Different TENDRA Comparisons                                                                                                   | 94 |

| 5.2        | Simulation parameters of the baseline multi-core system                                                                        | 96 |

| 5.3 | Workloads for Quad-Core System         |  |

|-----|----------------------------------------|--|

| 5.4 | The maximum write count of a LLC block |  |

## Chapter 1

## Introduction

This chapter presents a broad overview of the problems plaguing Spin Transfer Torque Random Access Memory based Last Level Caches. This chapter delves into the significance of the proposed works, offering a brief yet insightful summary of the principal ideas and contributions.

#### 1.1 Introduction

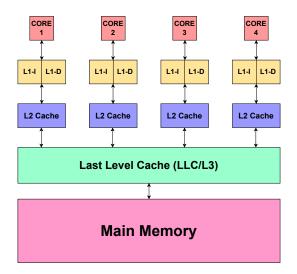

The advent of Machine Learning and Artificial Intelligence introduces data-intensive workloads that demand fast training and testing time. These workloads are distributed across multiple cores within the processor, all of which are integrated onto a single chip [2]. Multi-core architectures usually comprise a hierarchy of cache memories. The overall system's speed is highly dependent on the performance and capabilities of the caches as it provides a bridge to fill the gap in the performance difference between the slow Maim Memory and the fast processor. Cache memories are fast memories that can be placed on-chip. These memory systems operate on the principle of locality, storing data that is likely to be accessed in the near future. Modern commercial processors typically feature multiple levels of cache. The higher-level caches: L1 and L2 are exclusive to individual cores, while the Last Level Cache (LLC) is shared across all processing cores. The Level 1 (L1) cache is divided into two parts: the data cache (L1-D) and the instruction cache (L1-I). Figure 1.1 gives us an overview of the memory organization and hierarchy.

Figure 1.1: Memory Organization and Hierarchy.

Memory system design is increasingly scrutinized as architects tackle rising power demands. The growing costs of acquiring and operating large-scale supercomputers and data centers have highlighted the significant power consumption of memory subsystems, making them a central focus for efficiency improvements [3]. Supporting such workloads requires larger on-chip caches to minimize the off-chip data movement that incurs extra latency. CPU architectures have been revolutionized over the years, but the traditional cache architectures are not able to scale up as such, creating a performance bottleneck. Therefore, data-intensive workloads require larger memory systems and cost-effective alternative memory technologies that can help scale these memory systems. Traditionally, Static Random Access Memory (SRAM) has been used to design the on-chip caches. Major drawbacks of SRAM include a larger on-chip area and high leakage power. Previous studies [4] have indicated that leakage accounts for nearly 80% of the LLCs power consumption. Therefore, increasing the size of the SRAM based LLCs is not feasible with regard to power, area, and cost. Emerging memory technologies, such as embedded dynamic random access memory (eDRAM) [5], spin transfer torque random access memory (STT-RAM) [6], resistive random access memory (RRAM) [7], phase change memory (PCM) [8], and domain wall memory (DWM) [9], offer promising solutions to address these challenges due to their desirable features. When employed in the design of on-chip caches, these technologies offer significantly higher density and lower leakage compared to SRAM. This allows for reduced area and power consumption at equivalent capacities, or increased cache capacity within the same physical footprint [10].

#### 1.1.1 STT-RAM LLCs

STT-RAM based LLC can be considered as the most expected possible alternative to SRAM based LLC because of its compatibility with the processor's fabrication technology as it is made of similar materials. More details are given in Section 2. Although there are a lot of advantages that support the use of STT-RAM LLCs the major concern about it being accepted industry-wide is the limited write endurance of an STT-RAM cell [11]. This major concern is further heightened by non-uniform write patterns across the whole LLC in multi-core architectures. These non-uniform write patterns give rise to the write variations (WVs) in the LLC [12]. Due to the fluctuations in write patterns, applications create write hot spots within the cache. This causes some locations in the STT-RAM LLC to be written into more than normal. Therefore, those locations will wear out faster, resulting in a reduction in the lifetime of the STT-RAM LLCs. Uneven write variation can also be exploited in non-secure LLCs by attackers to target the LLC through an endurance attack to reduce its lifetime. Furthermore, write operations are problematic as they take a long time to be completed as compared to a read operation, therefore it creates a congestion in the read/write queue of the LLC because when the write operation is being serviced the read operations have to wait. Therefore, it results in a drop in the performance of the system [13].

## 1.1.2 Challenges and Solutions for implementing STT-RAM LLCs

The major challenge in implementing the STT-RAM as LLC is the write operation and the problems associated with it [14]. These include:

- 1. High Write Latency.

- 2. High Write Energy Consumption.

- 3. Low Write Endurance of an STT-RAM cell.

In order to deal with the problems caused by writes to the STT-RAM LLC, researchers have identified four principal types of solutions:

- Write Variation leveling (wear leveling) Enhances Endurance: These techniques aim to redistribute the writes evenly across the whole cache thereby reducing the maximum write count in a cache line [12, 15, 16, 14, 17, 18].

- Write Bypassing (write reduction) Reduces Write Latency: These techniques try to bypass writes that are not useful directly to the main memory such that it leads to decongestion in the read/write queue of the LLC [19, 20, 21, 13, 22].

- Hybrid Caches (write redirection) Enhances Endurance: It consists of two parts: a volatile section and a non-volatile section, and the majority of the techniques try to redirect the writes in the non-volatile section to the volatile section [23, 24, 25, 26, 27].

- Multi-retention time STT-RAM Reduce Write Energy Consumption: Here different types of STT-RAM cells are used with multiple retention times and thereby varying endurance. Lower retention time cells have higher endurance and low write energy consumption [28, 29, 30].

More details about these solutions and the different state-of-the-art approaches proposed are discussed in Chapter 2.

## 1.1.3 Write Variations

Write Variation in an STT-RAM based set-associative LLC is generally categorized as [12]:

- Inter-set Write Variation (InterV): InterV occurs exclusively within a cache set, arising from disproportionate write frequencies among the individual blocks contained within the specific cache set. Notably, certain blocks within the set undergo a higher volume of writes than others, resulting in accelerated wear for these heavily utilized blocks as compared to their counterparts.

- Intra-set Write Variation (IntraV): Conversely, IntraV denotes disparate write counts observed among cache sets, highlighting a lack of uniformity in data writing patterns across the cache sets. Consequently, this imbalance accelerates the degradation of heavily utilized sets, leading to their premature breakdown relative to their less active counterparts.

## 1.1.4 Wear Leveling Techniques

Over the years, a multitude of wear-leveling techniques have been proposed to reduce both InterV and IntraV, with the latter comprising the majority of research. Wang et al. [12] introduced Probabilistic Set Line Flush (PoLF), which implements write blocking to a designated block within the set. It designates a block as invalid following a predefined number of writes, known as the Flush Threshold (FT). Should the number of writes to the block exceed the FT, it is blocked for further write operations. Jokar et al. [15] introduce Write-back aware intra-set displacement (WAD), an approach for identifying and managing blocks within a set that experiences limited write traffic from the main memory, utilizing a sophisticated counter mechanism. The write-intensive blocks are subsequently exchanged with a victim block within the identical set, including a process to mitigate any substantial increase in the LLC miss ratio. EqualChance, outlined by Mittal et al. [16], adopts a method that involves the strategic swapping of write-intensive blocks within the cache set with those that are either invalid or clean. Agarwal et al. [14] propose three distinct methodologies: Static Window Write Restriction (SWWR), Dynamic Window Write Restriction (DWWR), and Dynamic Way Aware Write Restriction (DWAWR). The majority of these techniques are counter based techniques and are vulnerable to intelligent endurance attacks to some extent.

The main goal of this thesis is to propose efficient wear leveling techniques that will enhance the endurance of the STT-RAM LLC while reducing the write variations and not compromising too much on the performance. We also try to exploit the vulnerability of the wear leveling techniques with the help of unique targeted endurance attacks.

## 1.2 Motivation

All the wear leveling techniques have always been implemented to reduce the InterV and IntraV. They help in improving the lifetime of the system, but they always have a drawback of extra performance overhead that arises due to write redirection from the write hot cache lines to another cache line. The degradation in performance is a quite significant issue and hinders the efficiency of the system. Furthermore, there are write-bypassing techniques that focus on bypassing write from the read/write queue of the LLC. This will help in improving the congestion of the read/write queue which ultimately helps in improving the performance of the system. Therefore, in order to incorporate the benefits of enhanced endurance with performance improvement we have implemented techniques that do both write bypassing and wear leveling. As per our knowledge, this is the first work to pinpoint how the drawbacks of wear leveling can be effectively resolved by efficient priority-based intelligent write bypassing. Furthermore, the majority of the wear leveling techniques mainly focus on the set-level granularity wear leveling, i.e. reduction in InterV or way-level

granularity wear leveling, i.e. reduction in IntraV, but none of the works have targeted the block-level granularity wear leveling. Our work helps in implementing block-level wear leveling in an Optimal and Hardware Efficient manner. Furthermore, these counter based wear leveling techniques may be able to wear level writes in generic workloads, but they may not be effective against targeted endurance attacks that are intelligent with write patterns that can counteract the wear leveling techniques.

## 1.3 Summary and Organization of the Thesis

As previously stated above the main motivation of this thesis is to identify potential problems in implementing STT-RAM as LLCs and providing mitigation techniques in order to overcome these problems. Various state-of-the-art wear leveling techniques have been proposed over the years that mainly wear level the writes and improve the lifetime by reducing the InterV and IntraV of the LLC. The redirection caused due to wear leveling brings about some lifetime degradation. However, in this work we propose a technique that aims to dynamically reduce the write count and perform wear leveling. Furthermore, we also propose a wear leveling technique for block-level granularity that tries to perfectly even out the writes. A few vulnerabilities of implementing STT-RAM with and without wear leveling techniques have been exposed by proposing some innovative endurance attacks at the STT-RAM based LLC. The work in this thesis can be divided into three major parts:

- A) Literature Survey In this section, we present a comprehensive survey of various cache endurance challenges, which we categorize into four key areas: write variation leveling techniques (wear leveling), write bypassing techniques (write reduction), hybrid cache architectures, and LLC attacks.

- B) Lifetime Improvement in STT-RAM LLCs In this section, we have analyzed the effects of uneven write distribution on lifetime of STT-RAM based LLCs. Therefore, we have explored the possibility of wear leveling without redirection and just bypassing from write hot cache locations. The writes are bypassed either to a small SRAM buffer or to the Main Memory. The small SRAM buffer is used to store those writes that have high liveness score, this will help in reducing the miss penalty that will occur if we have to fetch a block from the Main Memory. This was done at the set level and way level granularity.

Furthermore, we also analyze the need for wear leveling at the block level granularity which is an improvement over set level wear leveling or way level wear leveling. It also looks into ways how to wear level the cache while preventing any timing channel attacks at LLC level. We propose two different techniques, one which employs a block wise write counter and wear levels the writes evenly, the other is a hardware efficient approach which clubs blocks into buckets and the writes are distributed among these buckets based on their write count.

C) Endurance Attacks on STT-RAM LLCs - This section shows the vulnerability of the STT-RAM LLCs against targeted endurance attacks even when implemented with wear leveling techniques.

Overall, the ideas proposed in this thesis provide efficient wear leveling techniques for lifetime improvement and also exploit the vulnerability of the STT-RAM LLC to introduce targeted endurance attacks. In order to keep this chapter short and simple, we have omitted a detailed discussion of these ideas. The organization of the thesis is outlined as follows:

- Chapter 1: Introduction This chapter provides a concise introduction to multi-core caches and explores the potential implementation of STT-RAM in LLCs. It also outlines the motivation behind this thesis and its overall workflow.

- Chapter 2: Background and Literature Review This chapter covers essential background information and includes a comprehensive literature survey (Part A).

- Chapter 3: Dynamic Write Bypassing for Lifetime Improvement in STT-RAM LLCs This chapters discusses the ideas proposed as Part B above.

- Chapter 4: Decoupling the tag and data array for Lifetime Improvement

This chapter explains the ideas of Part B as mentioned above.

- Chapter 5: Endurance Attacks on STTRAM LLCs This chapter discusses the idea of above mentioned Part C.

- Chapter 6: Conclusion and Future Work This thesis is concluded in this chapter.

## Chapter 2

## Background and Literature Review

In this chapter, we have explored essential background information relevant to this thesis. It is also accompanied by a comprehensive literature review on non-volatile memory-based cache endurance. The chapter concludes with a summary of the limitations in current techniques and highlights the significance of the contributions made in this thesis.

## 2.1 Background

This section highlights the characteristics of STT-RAM, the NVM that we have used to design the LLC. It further discusses the challenges in implementing STT-RAM LLCs and the architectural changes required to build the same. Some generic studies in NVM like [31, 32, 33] have pointed out the challenging areas that need to be addressed.

#### 2.1.1 Cache Memories

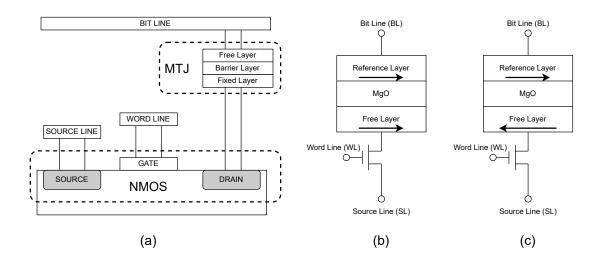

Modern processors are designed with multiple levels of cache to enhance memory access speed and minimize latency. In most contemporary processors, each core is equipped with private upper-level caches, while the LLC is shared among all cores. The caches considered in this work are set-associative, meaning each cache contains a fixed number of sets. A block is mapped to a specific set based on the set-index bits derived from the block's address, and the number of blocks that can reside in a set is determined by the cache's associativity. In an N-way set-associative cache, each set can hold N blocks. Throughout this thesis, N represents the cache's associativity, and M denotes the number of sets in the LLC. Figure 2.1 depicts the structure of the set-associative cache that is used as the LLC.

To access data in the cache, a memory address is divided into three components: the tag, block offset, and set index. The set index indicates the set where the block is located, the tag uniquely identifies the block within that set, and the offset specifies the location of the data within the block. It's important to note that while the L1 cache is typically virtually indexed—using the virtual address to determine the set index—the LLC is usually physically indexed, meaning the set index is derived from the physical address.

A cache replacement policy is employed to manage the selection of cache entries for eviction when a new block needs to be inserted into a non-empty set. Such a policy consists of three key components: *insertion*, *promotion*, and *eviction*. The insertion component determines where a newly arrived block will be placed in the cache. The promotion component activates upon a cache hit, boosting the priority or position of the accessed block. The

Figure 2.1: A generic Set-Associative LLC.

eviction component is responsible for selecting a block, known as the *victim block*, for replacement when necessary. In standard replacement policies, any process can evict another process's block if it is chosen as the victim. However, when processes are not permitted to evict each other's blocks, they are considered to be isolated within the cache. A LLC can be designed as inclusive, exclusive, or non-inclusive. In an inclusive LLC, the cache contains all the blocks stored in the upper-level private caches, meaning any block evicted from the LLC must also be removed from the private caches to maintain this inclusivity. In contrast, an exclusive LLC does not duplicate blocks held in the private caches, with directories used within the LLC to ensure cache coherence and track which blocks are present in the private caches. A non-inclusive cache configuration does not strictly enforce inclusion, allowing for more flexibility—blocks may reside in both the LLC and private caches, but this is not guaranteed.

Understanding these cache architectures is essential for analyzing the problem of endurance of an STT-RAM LLC and the mitigation strategies and attack directions that have been proposed.

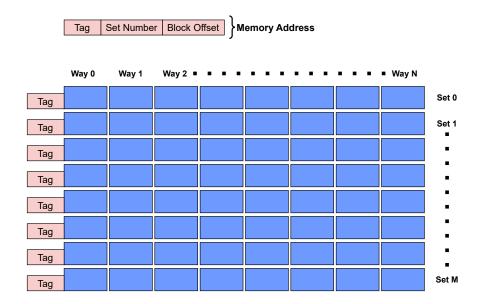

#### 2.1.2 STT-RAM Cell

Figure 2.2 (a) shows the conceptual layout of an STT-RAM cell. This cell comprises of an access transistor alongside a Magnetic Tunnel Junction (MTJ). The MTJ structure consists of a tunnel barrier, composed of MgO, sandwiched between two ferromagnetic layers. The reference layer, possesses a fixed magnetization direction. Conversely, the magnetization direction of the other layer, termed the free layer, is variable and can be altered by a spin-polarized current. The tunnel barrier serves as a thin insulating layer separating the two ferromagnetic layers. These layers magnetization directions encode the stored data bit within the cell. Specifically, when the magnetization directions are

Figure 2.2: Layout of an STT-RAM cell.

anti-parallel, the resulting high resistance represents a logical '1' as shown in Figure 2.2 (c), whereas parallel magnetization denotes a logical '0' with low resistance as shown in Figure 2.2 (b).

Both read and write operations in an STT (Spin-Transfer Torque) memory cell are executed by manipulating the voltage differential between the source and a bit-line. Writing a '0' in the STT cell requires applying a significant positive voltage across the source and the bit-line, which induces a current that alters the magnetic orientation of the cell, setting it to the desired state. To write a '1', a substantial negative voltage is applied, reversing the magnetic polarity to reflect the '1' state.

In contrast, the read operation involves applying a smaller voltage across the source and the bit-line, generating a current that flows through the cell. This current is then compared against a reference current, allowing the system to determine whether the cell holds a '0' or '1'. By carefully measuring this current relative to the reference, the memory state is accurately identified without disrupting the stored data.

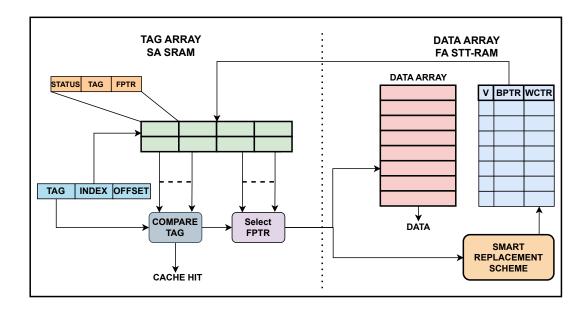

## 2.1.3 STT-RAM based LLC

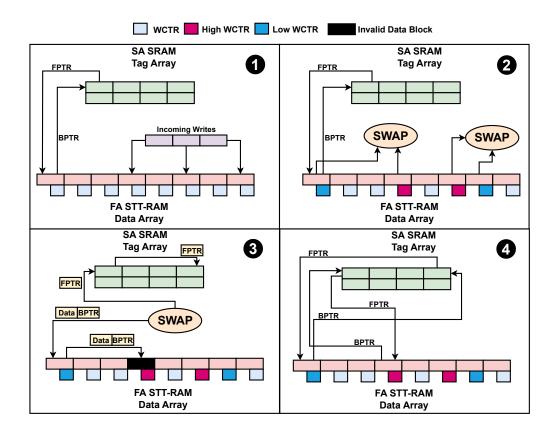

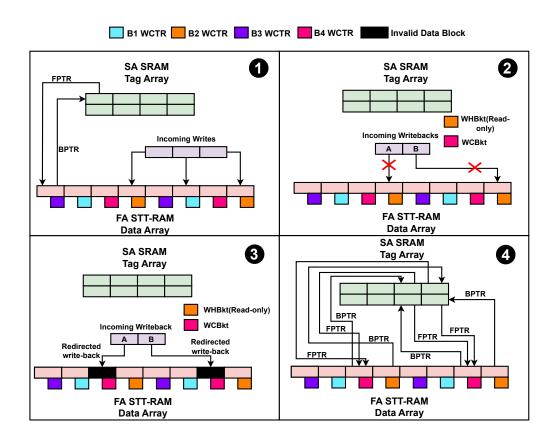

STT-RAM provides numerous advantages compared to traditional SRAM-based LLCs [10]. Table 2.1 highlights the key characteristics of an STT-RAM cell in comparison to an SRAM cell. The parameter F in the table denotes the smallest feature size achievable within a specific technology node, offering a direct comparison of the cells' properties under equivalent conditions. This comparison provides insight into the differences in performance, scalability, and efficiency between STT-RAM and SRAM technologies.

Although STT-RAM boasts numerous advantages over SRAM, including smaller cell size, reduced leakage power, and extended retention time, as illustrated in Table 2.1, it has a few drawbacks. These benefits must be weighed against certain inherent disadvantages accompanying STT-RAM technology, which may impact its overall suitability. The primary challenge for on-chip memory systems that rely on STT-RAM based LLCs is the

| Parameters          | SRAM      | STT-RAM            |

|---------------------|-----------|--------------------|

| Cell $Size(F^2)$    | 120-200   | 6-50               |

| Write Endurance     | $10^{16}$ | $4 \times 10^{12}$ |

| Speed(Read/Write)   | Very Fast | Very Fast/Slow     |

| Leakage Power       | High      | Low                |

| Dynamic Energy(R/W) | Low       | Low/High           |

| Retention Period    | Very Low  | High               |

Table 2.1: Comparison of SRAM cell and STT-RAM cell (R/W=Read/Write).

significantly higher write latency and energy consumption associated with write operations compared to the traditional SRAM. While STT-RAM offers several advantages, these elevated write metrics can hinder its overall performance and efficiency, making it a critical factor to consider in the design of memory architectures. This trade-off between the benefits of STT-RAM and its inherent write-related drawbacks is a key consideration in determining its viability for widespread implementation.

## 2.2 Write Variation and Lifetime

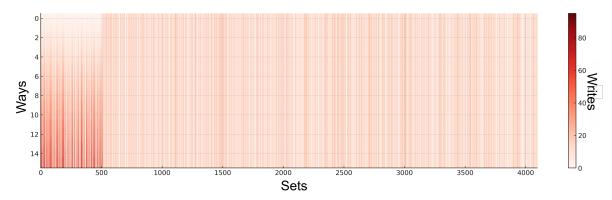

Write variation (WV) presents a substantial challenge in the design of cache and non-volatile memory technologies. When write operations are unevenly distributed across the memory cells, certain areas experience a much higher frequency of writes than others. This imbalance accelerates wear and tear on those heavily written areas, leading to premature degradation of the memory cells. As a result, the overall lifespan of the cache is significantly diminished, compromising the reliability and effectiveness of the memory system. Addressing WV is crucial for ensuring that these technologies can maintain their performance and longevity in real-world applications. Even a small fraction of heavily written memory cells can render an entire cache or memory system inoperative, despite the majority of cells being far from wear-out. Our work focuses on minimizing the WV in the STT-RAM LLC. WV in an NVM-based set-associative LLC is generally categorized as:

- a) Inter-set Write Variation (InterV)

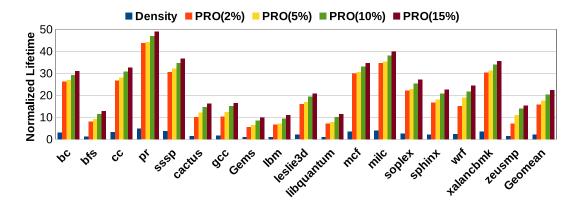

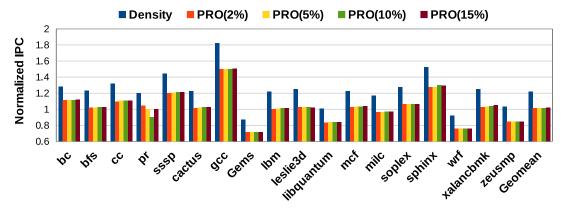

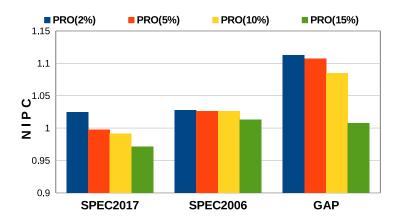

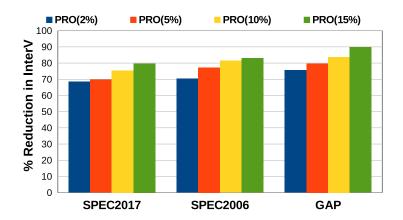

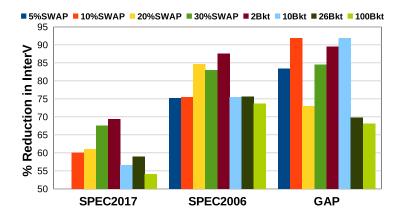

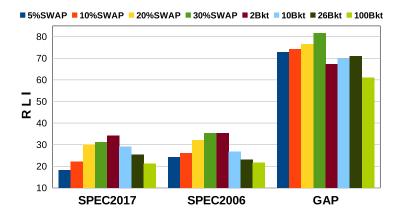

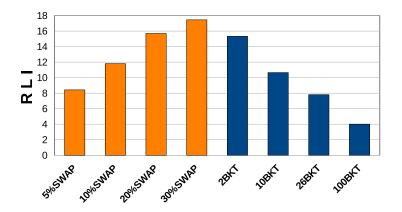

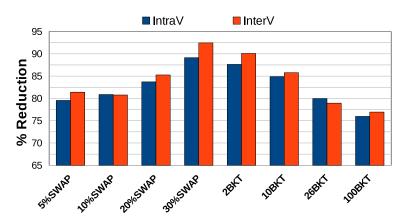

- b) Intra-set Write Variation (Intra V)